# ANTAIOS User Manual

ANT1000/1001 | Revision 1.19

#### Liability Exclusion

We have tested the contents of this document regarding agreement with the hardware and software described. Nevertheless, there may be deviations and we do not guarantee complete agreement. The data in the document is tested periodically, however. Required corrections are included in subsequent versions. We gratefully accept suggestions for improvements.

#### Copyright

Copyright © YASKAWA Europe GmbH 2020. All Rights Reserved.

Unless permission has been expressly granted, passing on this document or copying it, or using and sharing its content are not allowed. Offenders will be held liable. All rights reserved, in the event a patent is granted or a utility model or design is registered.

This document is subject to changes without prior notice.

| 1 | Intr | oduction                                | 22 |

|---|------|-----------------------------------------|----|

|   | 1.1  | ARM Cortex-A5 CPU Core                  | 22 |

|   | 1.2  | Advanced Real-Time Ethernet Switch      | 22 |

|   | 1.3  | Integrated 100BaseTX Ethernet PHYs (2x) | 23 |

|   | 1.4  | SNAP+ (SliceBus) Master                 | 23 |

|   | 1.5  | Gigabit Ethernet MAC                    | 24 |

|   | 1.6  | DDR2 16 bit Controller                  | 24 |

|   | 1.7  | Asynchronous External Interface (AEI)   | 24 |

|   | 1.8  | FIFO Interface                          | 24 |

|   | 1.9  | Consistency Interface (CI)              | 24 |

|   | 1.10 | PROFIBUS-DP Master (2x)                 | 25 |

|   | 1.11 | VPC3+ PROFIBUS-DP Slave                 | 25 |

|   | 1.12 | CAN Interface (2x)                      | 25 |

|   | 1.13 | NAND Flash Controller                   | 25 |

|   | 1.14 | QuadSPI Interface                       | 25 |

|   |      | SD/MMC Card Controller                  |    |

|   | 1.16 | USB 2.0 Device Controller               | 26 |

|   | 1.17 | Advanced IRQ Controller                 | 26 |

|   |      | Main DMA Controller                     |    |

|   |      | AHB/APB Bridge (2x)                     |    |

|   |      | SPI Interface                           |    |

|   |      | UART (2x)                               |    |

|   |      | I <sup>2</sup> C Interface              |    |

|   |      | Timer and Watchdog Module               |    |

|   |      | Boot Code                               |    |

|   | 1.25 | Technology Function Module (TechIO)     | 28 |

| 2 | Blo  | ck Diagram                              | 29 |

| 3 | AH   | B/APB Memory Mapping                    | 30 |

| 4 | Pin  | Controller                              | 32 |

| 5 | SN   | AP+ (SliceBus) Master                   | 35 |

| 6 | Gio  | abit Ethernet Controller                | 36 |

|   | 6.1  | Overview                                |    |

|   | 6.2  | Memory Map and Register Definition      |    |

|   | 6.3  | Function Description                    |    |

|   | 6.4  | Initialization Information              |    |

|   |      |                                         |    |

| 7 | DD   | R2 Memory Controller                    | 79 |

|   | 7.1  | Overview                                |    |

|   | 7.2  | Memory Map and Register Definition      | 86 |

|    | 7.3        | Memory Address Table (MA Table)              |     |

|----|------------|----------------------------------------------|-----|

|    | 7.4        | Miscellaneous                                |     |

| 8  | Asy        | nchronous External Interface (AEI)           | 125 |

|    | 8.1<br>8.2 | AEI configuration registersAEI read transfer |     |

|    | 8.3        | AEI write transfer                           |     |

|    | 8.4        | AEI data areas                               | 129 |

|    | 8.5        | Timing considerations                        | 130 |

| 9  | VPC        | C3+ Profibus DP V2 Slave                     | 131 |

| 10 | CAI        | N                                            | 132 |

|    | 10.1       | Overview                                     | 132 |

|    |            | Memory Map and Register Definition           |     |

|    | 10.3       | Functional Description                       | 145 |

| 11 | NAI        | ND Flash Controller                          | 157 |

|    | 11.1       | Overview                                     | 158 |

|    |            | Memory Map and Register Definition           |     |

|    |            | Initial Steps                                |     |

|    | 11.4       | Command Queue Access Method                  | 207 |

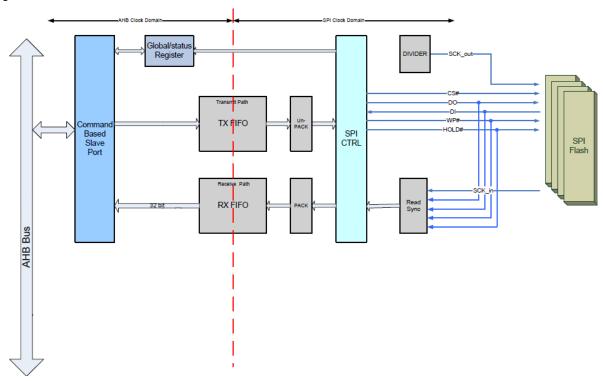

| 12 | Qua        | adSPI Channel                                | 209 |

|    | 12.1       | Overview                                     | 210 |

|    | 12.2       | Memory Map and Register Definition           | 216 |

| 13 | SD/        | MMC Card Controller                          | 223 |

|    | 13.1       | Overview                                     | 224 |

|    | 13.2       | DMA Transaction                              | 225 |

|    |            | SD Command and Data Input/Output Timing      |     |

|    |            | CPRM Operation                               |     |

|    |            | Memory Map and Register Definition           |     |

|    |            | Initialization/Application Information       |     |

| 14 | USE        | B Device Controller                          | 282 |

|    | 14.1       | Overview                                     | 283 |

|    |            | USB Rest and Power-saving Mode               |     |

|    |            | Memory Map and Register Definition           |     |

|    |            | Programming Guide                            |     |

| 15 | Adv        | anced IRQ Controller                         | 323 |

|    | 15.1       | Interrupt Sources                            | 323 |

|    | 15.2       | Register Mapping                             | 325 |

|    | 15.3 Register Description                    | 326 |

|----|----------------------------------------------|-----|

| 16 | DMA Controller                               | 340 |

|    | 16.1 Overview                                |     |

|    | 16.3 Register Definition                     |     |

|    | 16.4 Programming Guidelines                  |     |

| 17 | APB_Bridge                                   | 372 |

|    | 17.1 Overview                                | 372 |

|    | 17.2 Memory Map and Register Definition      | 374 |

|    | 17.3 Initialization                          | 379 |

| 18 | Serial Peripheral Interface Controller (SPI) | 381 |

|    | 18.1 Overview                                | 382 |

|    | 18.2 SPI Operation                           |     |

|    | 18.3 Register Definition                     |     |

|    | 18.4 Programming Guidelines                  | 395 |

| 19 | UART                                         | 399 |

|    | 19.1 Overview                                | 399 |

|    | 19.2 Memory Map and Register Definition      | 400 |

| 20 | I <sup>2</sup> C Bus Interface Controller    | 413 |

|    | 20.1 Overview                                | 413 |

|    | 20.2 Memory Map and Register Definition      |     |

|    | 20.3 Programming Guide                       | 419 |

| 21 | Timer and Watchdog Unit                      | 422 |

|    | 21.1 Timer                                   | 422 |

|    | 21.2 Watchdog                                | 434 |

| 22 | General Purpose I/O                          | 438 |

|    | 22.1 Programming Model                       | 438 |

| 23 | TechIO                                       | 442 |

|    | 23.1 IO-Pinning                              | 442 |

|    | 23.2 Digital input and output data           |     |

|    | 23.3 Filter                                  |     |

|    | 23.4 Alarm system digital input              |     |

|    | 23.5 Counter                                 |     |

|    | 23.6 Pulse width modulation (PWM)            |     |

|    | 23.7 Synchronous serial interface (SSI)      |     |

|    | 23.8 Alarm system technology function        | 480 |

# **Table of Contents**

| 494 |

|-----|

| 490 |

| 488 |

|     |

# **List of Figures**

| <b>J</b>     |                                                                 |     |

|--------------|-----------------------------------------------------------------|-----|

| Figure 2-1   | ANTAIOS Block Diagram                                           | 29  |

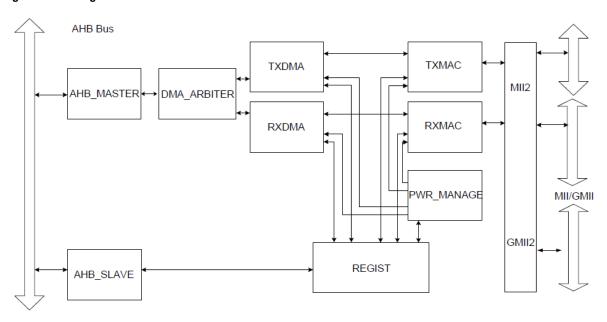

| Figure 6-1   | Gigabit Ethernet Controller                                     | 37  |

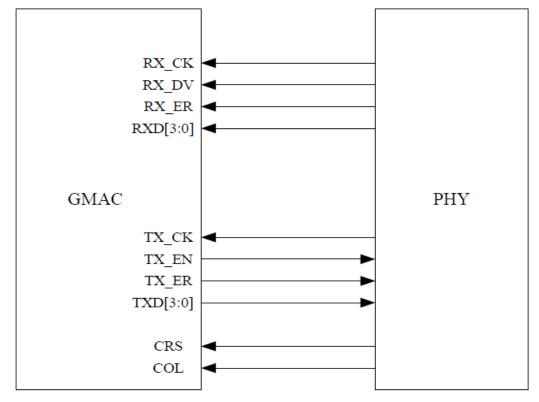

| Figure 6-2   | MII Connection                                                  | 62  |

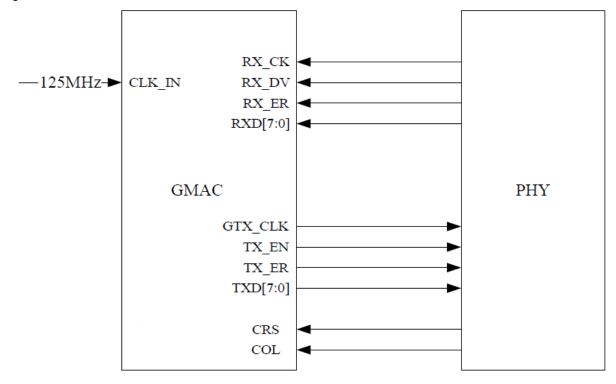

| Figure 6-3   | GMII Connection                                                 | 62  |

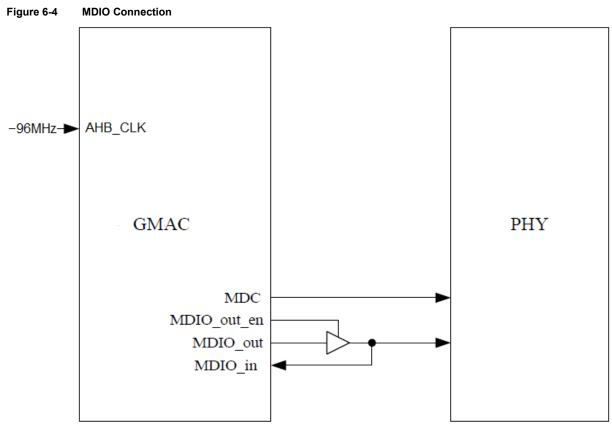

| Figure 6-4   | MDIO Connection                                                 | 63  |

| Figure 6-5   | Transmit Ring Descriptor Structure                              | 64  |

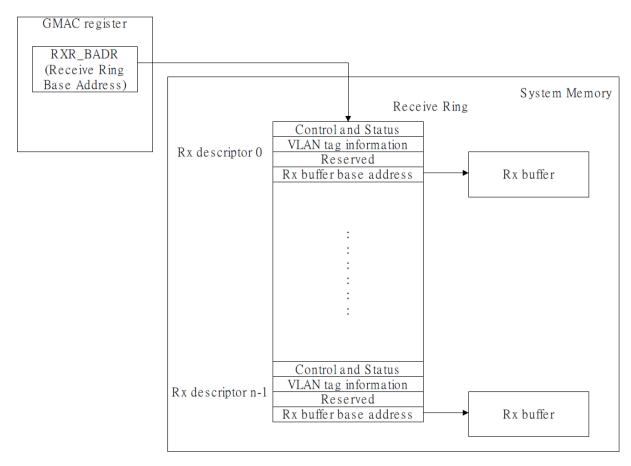

| Figure 6-6   | Receive Ring Descriptor Structure                               | 67  |

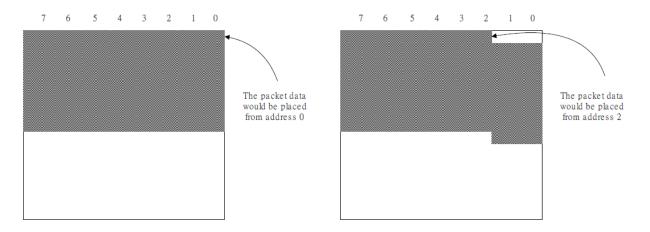

| Figure 6-7   | Packet Data Placement for Different Receive Buffer Address      | 74  |

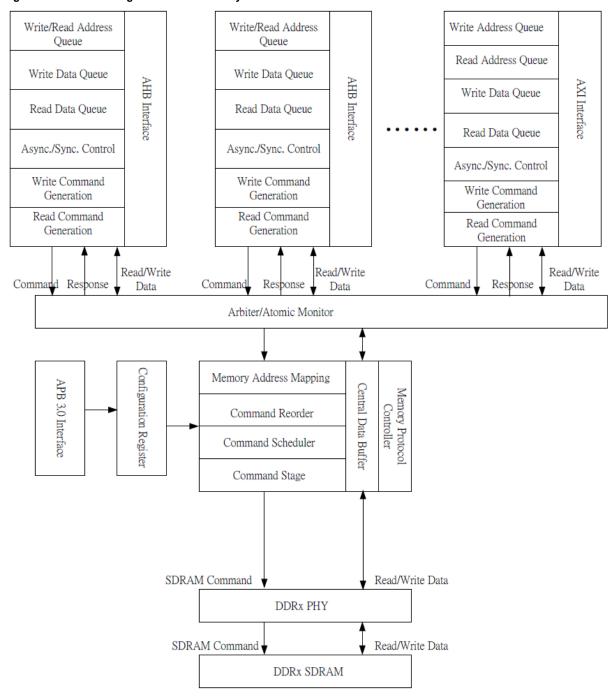

| Figure 7-1   | Block diagram of DDR2 Memory Controller                         | 80  |

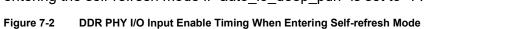

| Figure 7-2   | DDR PHY I/O Input Enable Timing When Entering Self-refresh Mode | 98  |

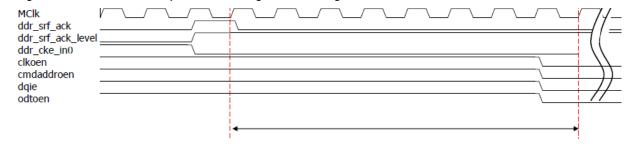

| Figure 7-3   | DDR PHY I/O Input Enable Timing When Exiting Self-refresh Mode  | 99  |

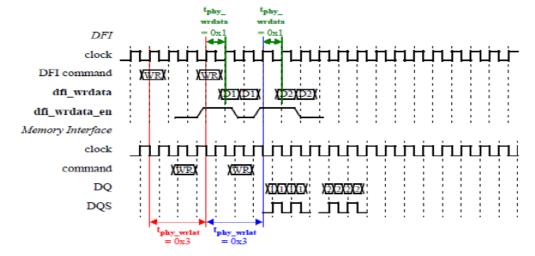

| Figure 7-4   | tphy_wrlat and tphy_wrdata Timing in DFI Specification 2.1      | 104 |

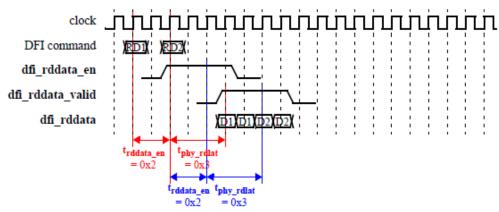

| Figure 7-5   | trddata_en and tphy_rdlat in DFI Specification 2.1              | 105 |

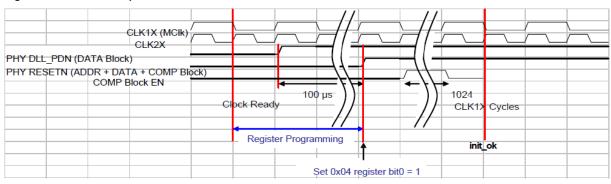

| Figure 7-6   | Reset Sequence of DDR2 PHY                                      |     |

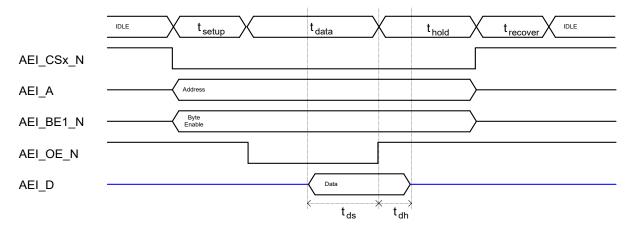

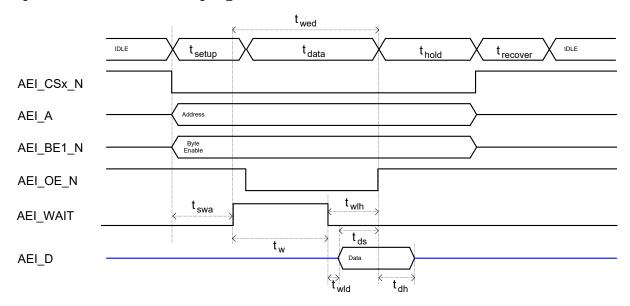

| Figure 8-1   | AEI read transfer                                               | 126 |

| Figure 8-2   | AEI read transfer using AEI_WAIT                                | 127 |

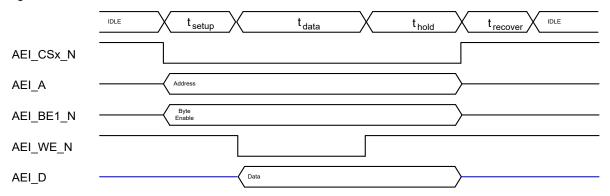

| Figure 8-3   | AEI write transfer                                              |     |

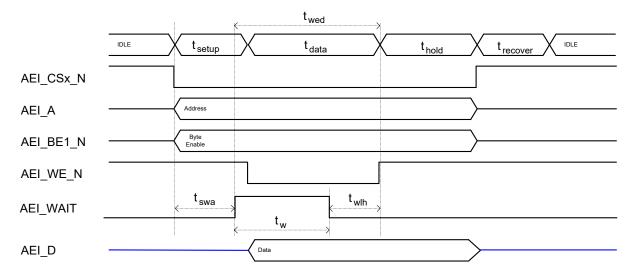

| Figure 8-4   | AEI write transfer using AEI_WAIT                               | 129 |

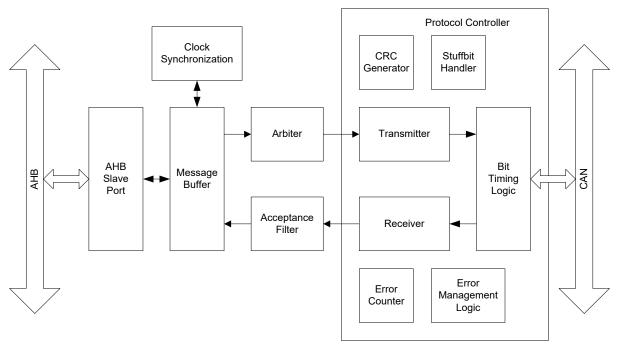

| Figure 10-1  | CAN Module                                                      |     |

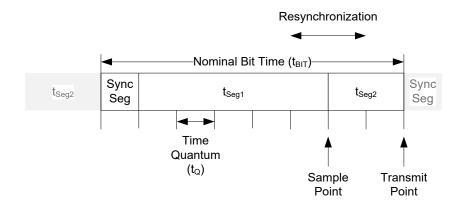

| Figure 10-2  | Bit Timing (shown for 1 Mbit/s)                                 | 139 |

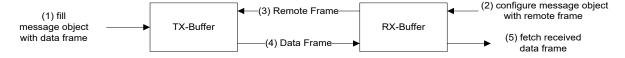

| Figure 10-3  | Data Frame                                                      | 145 |

| Figure 10-4  | Remote Frame with automatic Reply                               | 145 |

| Figure 10-5  | Remote Frame w/o automatic Reply                                | 146 |

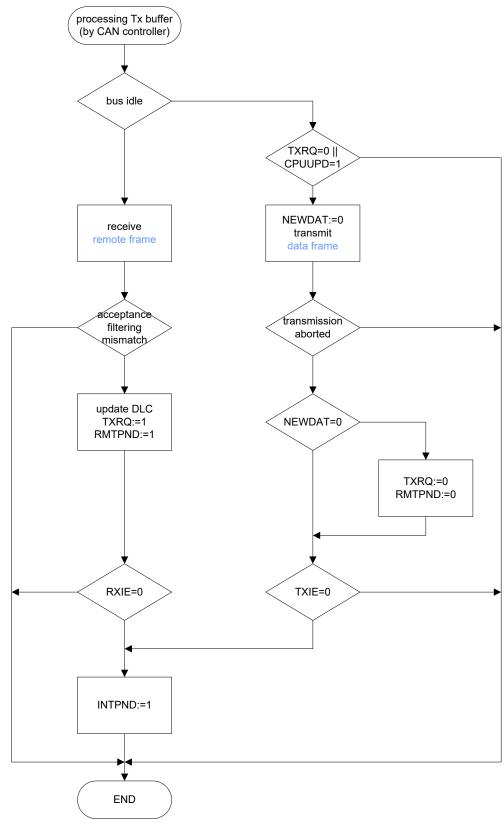

| Figure 10-6  | CAN Module Handling of Transmit Message Object                  | 148 |

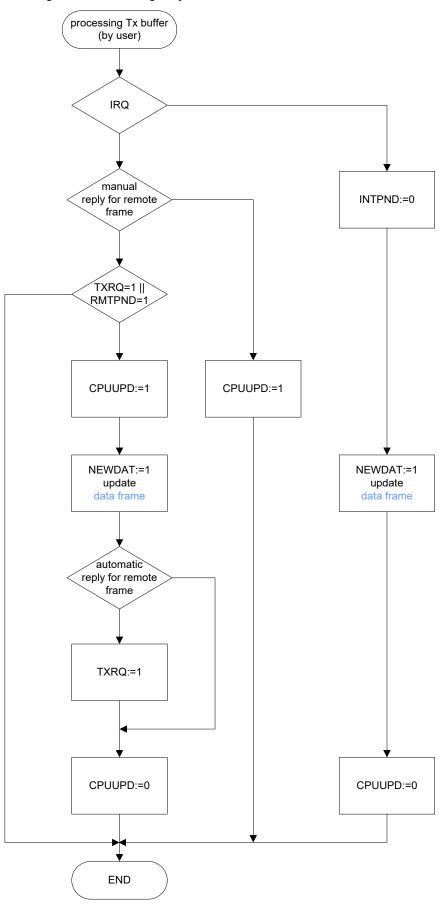

| Figure 10-7  | User Handling of Transmit Message Object                        |     |

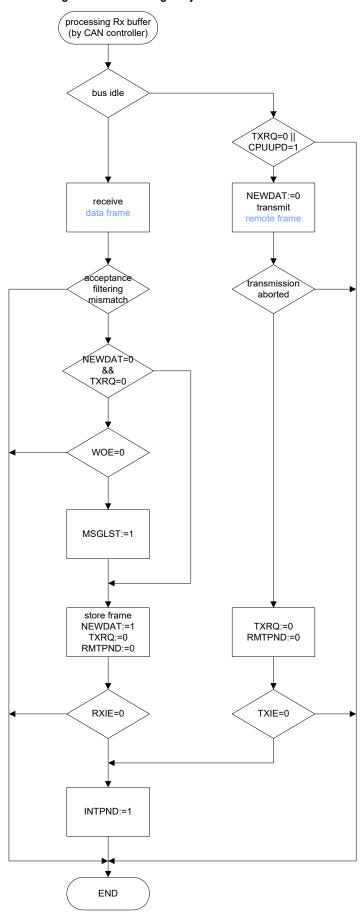

| Figure 10-8  | CAN Module Handling of Receive Message Object                   |     |

| Figure 10-9  | User Handling of Receive Message Object                         |     |

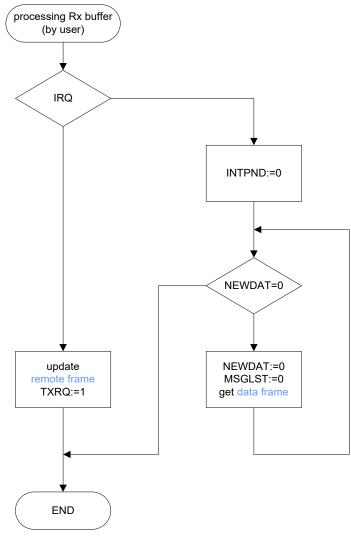

| Figure 10-10 | User Handling of interrupt                                      |     |

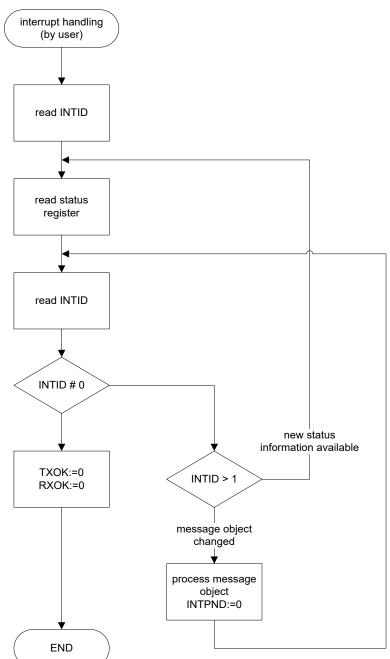

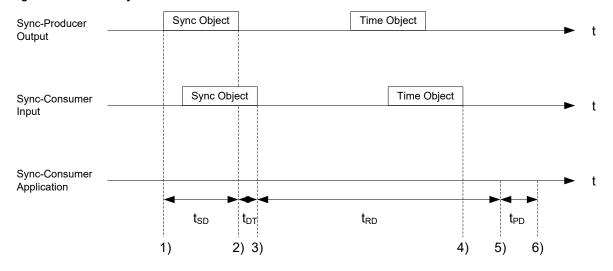

| Figure 10-11 | Clock Synchronization Mechanism                                 |     |

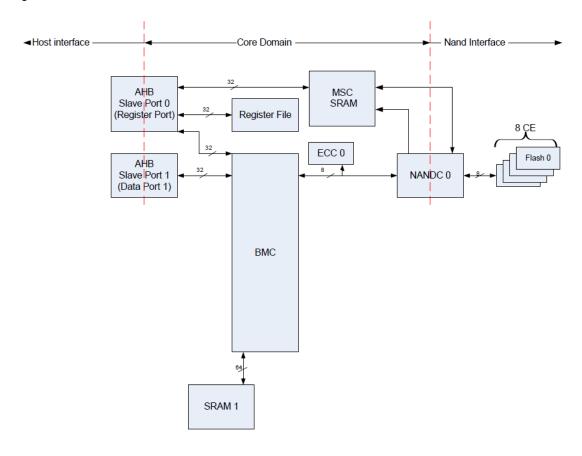

| Figure 11-1  | NAND Controller                                                 | 158 |

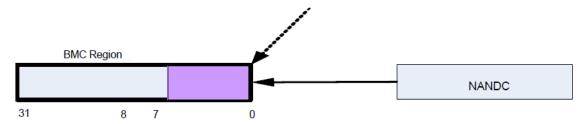

| Figure 11-2  | User Mode Operation                                             | 159 |

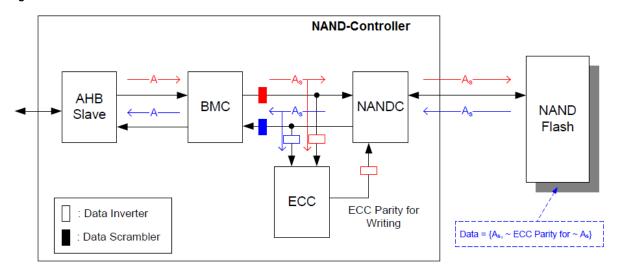

| Figure 11-3  | Scramble and data inverter                                      | 161 |

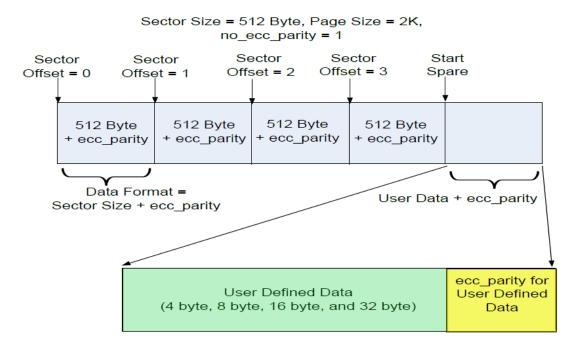

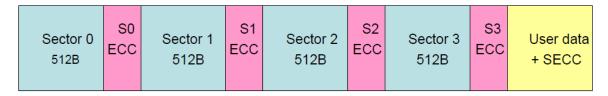

| Figure 11-4  | Data Format at no ecc parity = '0'                              | 162 |

| Figure 11-5  | User data and ECC usages                                        | 163 |

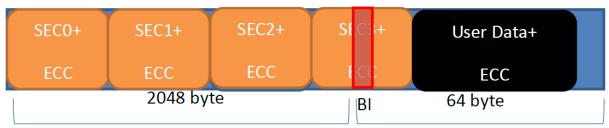

| Figure 11-6  | BI area                                                         | 163 |

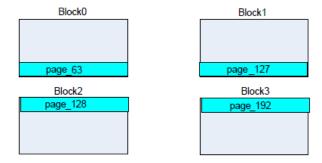

| Figure 11-7  | 2-plane write 4 pages cross block                               | 168 |

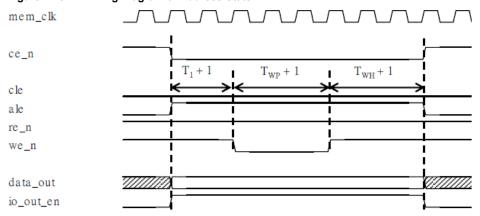

| Figure 11-8  | Timing Diagram of Address State                                 | 191 |

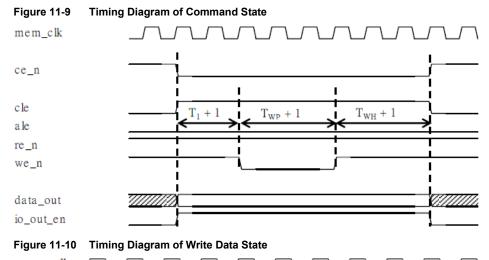

| Figure 11-9  | Timing Diagram of Command State                                 | 192 |

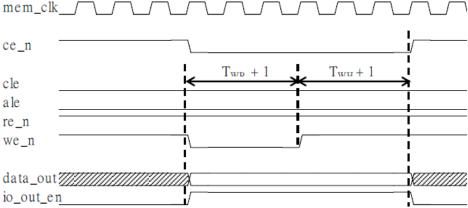

| Figure 11-10 | Timing Diagram of Write Data State                              |     |

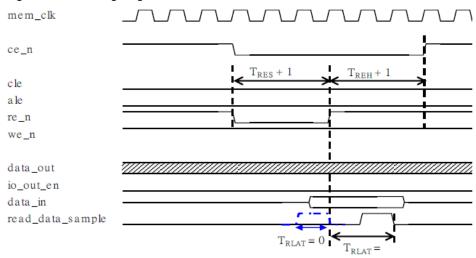

| Figure 11-11 | Timing Diagram of Read Data State                               |     |

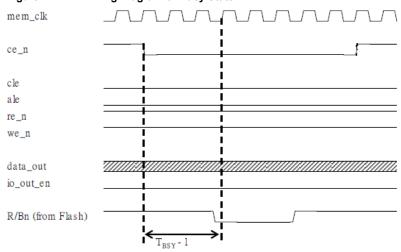

| Figure 11-12 | Timing Diagram of Busy State                                    |     |

| Figure 12-1  | QuadSPI Controller                                              |     |

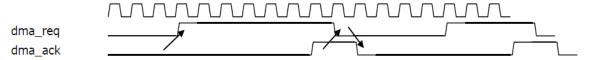

| Figure 12-2  | DMA Handshake Mode                                              |     |

| -            |                                                                 |     |

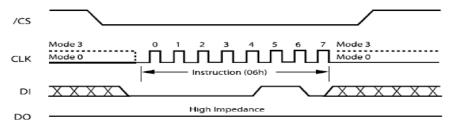

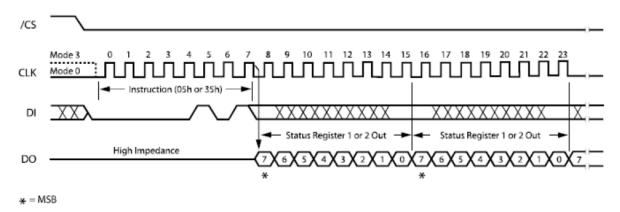

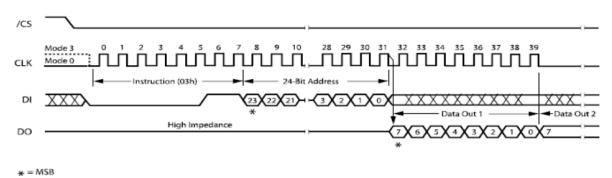

| Figure 12-3  | Write Enable                                                    | 211       |

|--------------|-----------------------------------------------------------------|-----------|

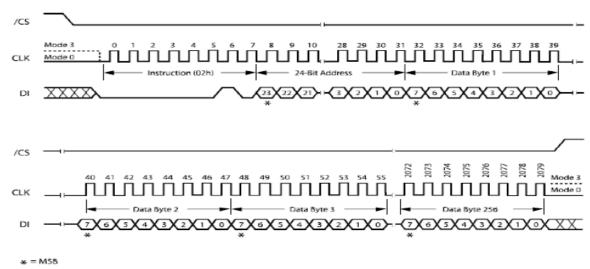

| Figure 12-4  | Page Program                                                    | 212       |

| Figure 12-5  | Read Status                                                     | 212       |

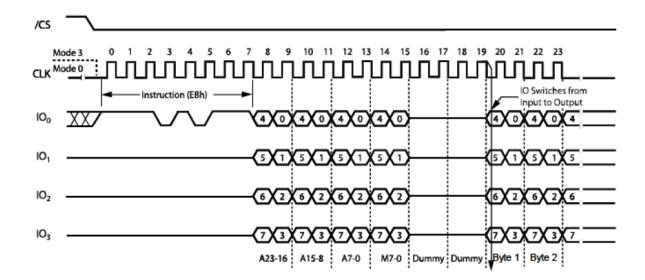

| Figure 12-6  | Read Data                                                       | 212       |

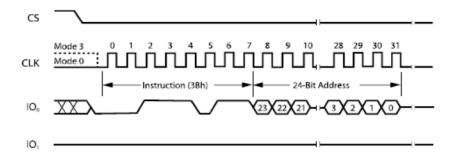

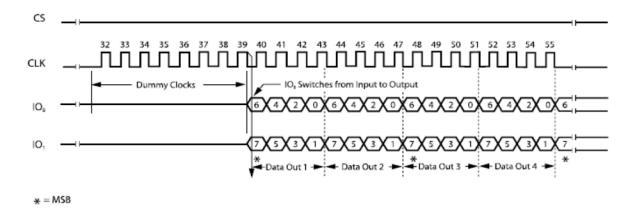

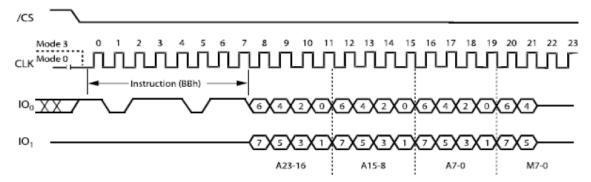

| Figure 12-7  | Fast Read Dual Output Command                                   | 213       |

| Figure 12-8  | Fast Read Dual I/O                                              | 214       |

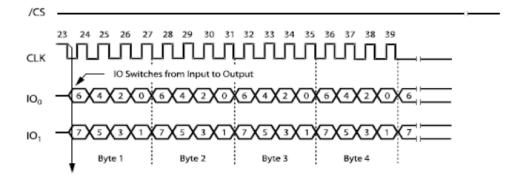

| Figure 12-9  | Fast Read Quad Output                                           | 215       |

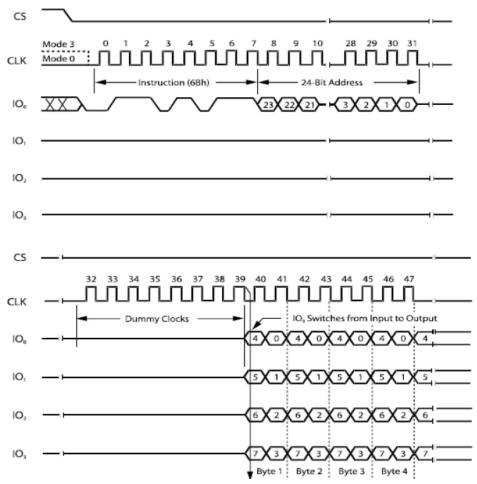

| Figure 12-10 | Fast Read quad_io Command                                       | 215       |

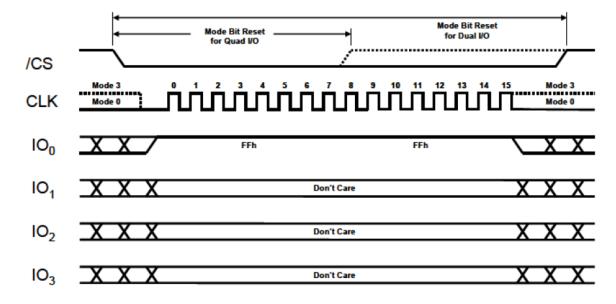

| Figure 12-11 | Continuous Read Mode Reset                                      | 216       |

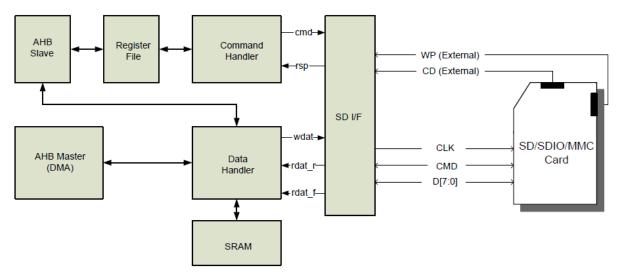

| Figure 13-1  | Block diagram of SD Card Controller                             | 224       |

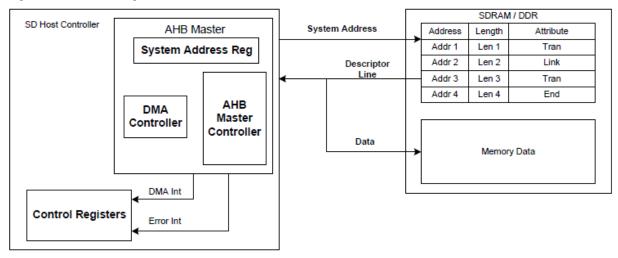

| Figure 13-2  | Block diagram of ADMA                                           | 226       |

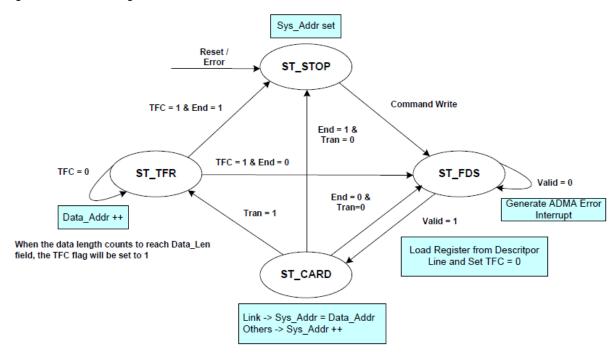

| Figure 13-3  | State Diagram ADMA                                              | 228       |

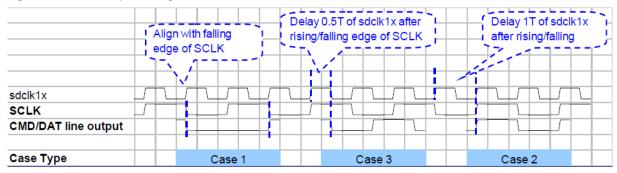

| Figure 13-4  | SD Output Timing                                                | 229       |

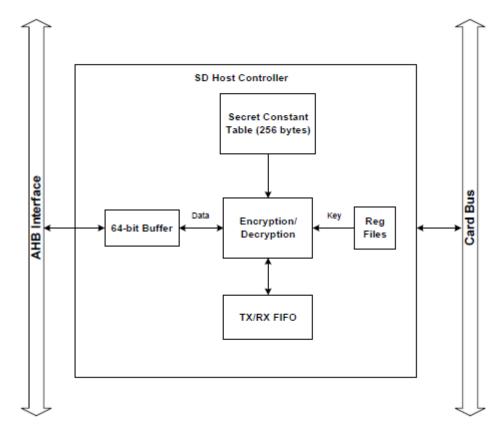

| Figure 13-5  | Host Controller with CPRM Function                              | 230       |

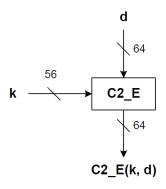

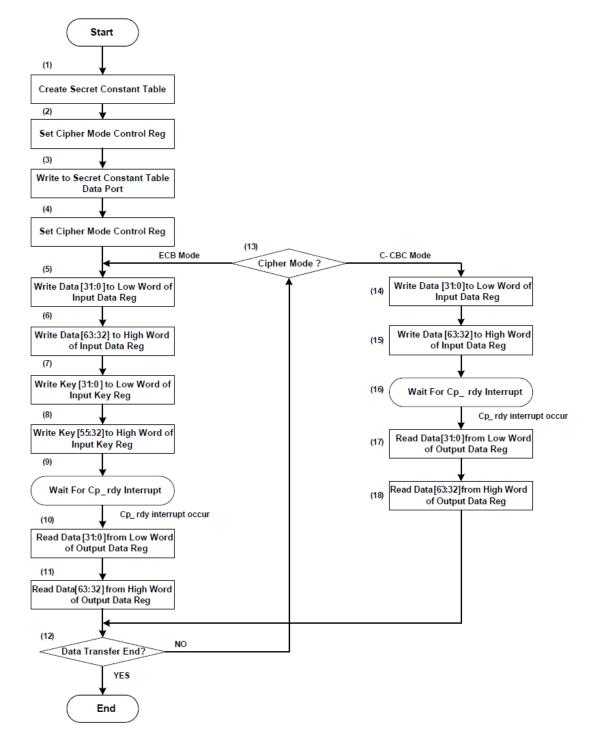

| Figure 13-6  | Encryption in ECB Mode                                          | 231       |

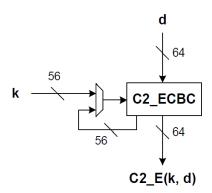

| Figure 13-7  | Encryption in C-CBC Mode                                        | 232       |

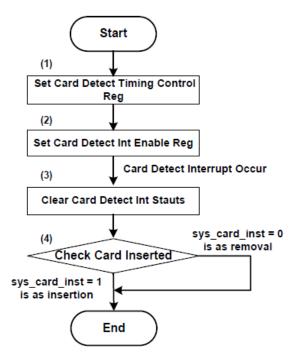

| Figure 13-8  | Card Detect Sequence                                            | 263       |

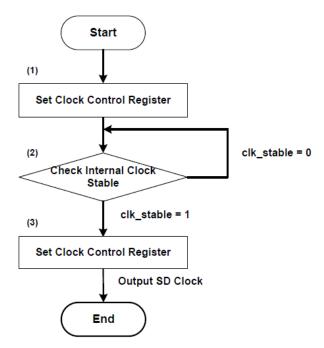

| Figure 13-9  | SD Clock Control Sequence                                       | 264       |

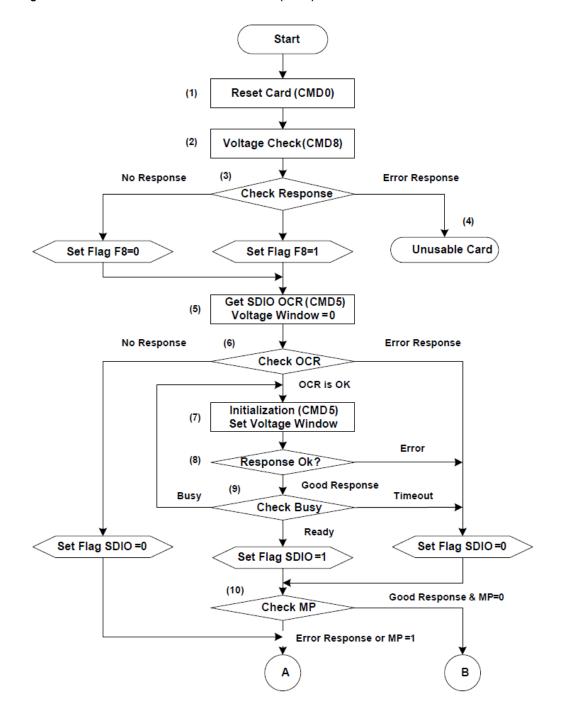

| Figure 13-10 | Card Initialization and Identification (PartA)                  | 266       |

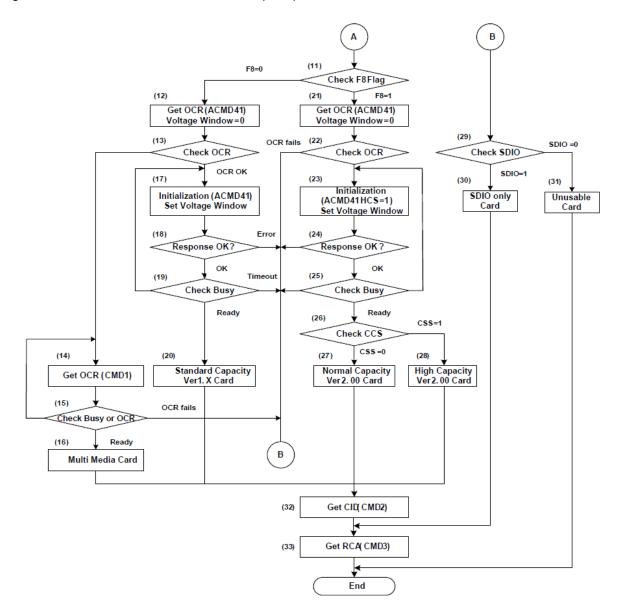

| Figure 13-11 | Card Initialization and Identification (PartB)                  | 267       |

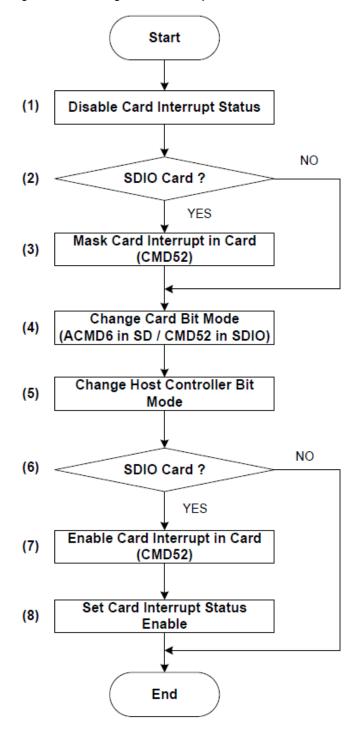

| Figure 13-12 | Change Bus Width Sequence                                       | 268       |

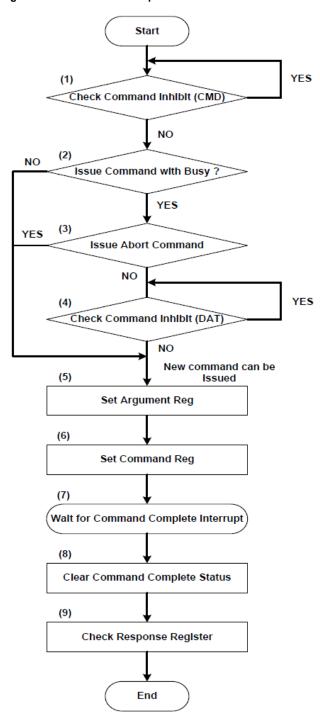

| Figure 13-13 | Command Sequence                                                | 270       |

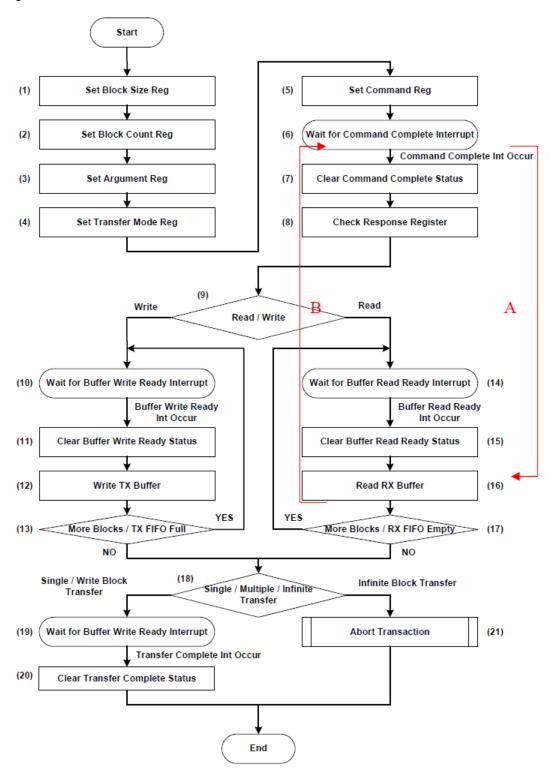

| Figure 13-14 | Data Transfer without DMA                                       | 272       |

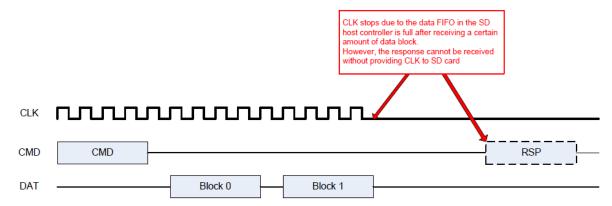

| Figure 13-15 | Command complete timeout, because of a full FIFO                | 273       |

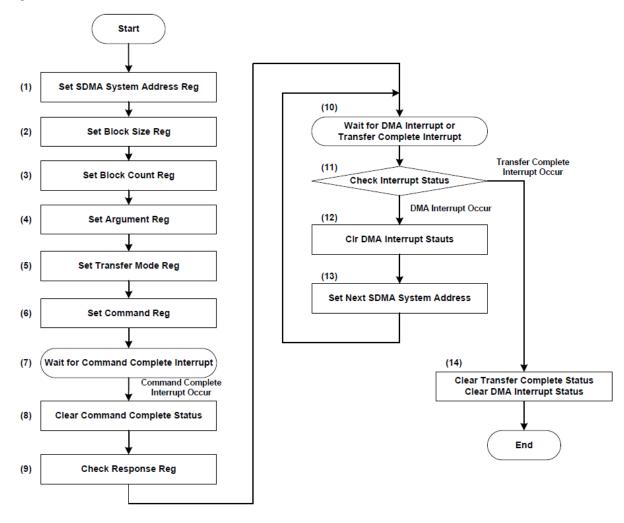

| Figure 13-16 | Data Transfer with SDMA                                         | 274       |

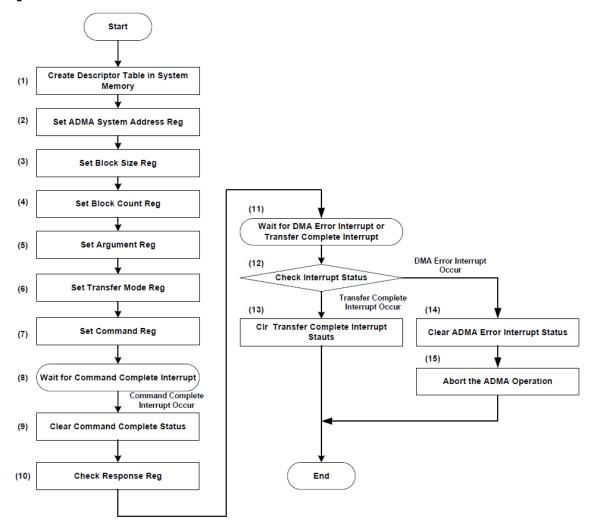

| Figure 13-17 | Data Transfer with ADMA                                         | 275       |

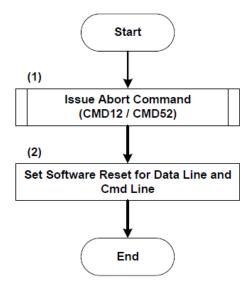

| Figure 13-18 | Asynchronous Abort Sequence                                     | 276       |

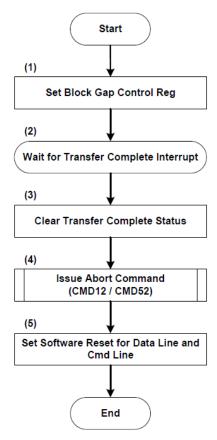

| Figure 13-19 | Synchronous Abort Sequence                                      | 277       |

| Figure 13-20 | Non-auto Mode CPRM Sequence                                     | 279       |

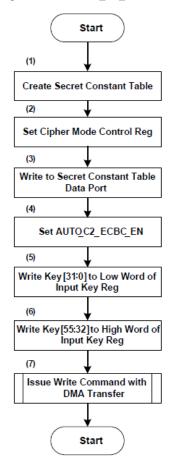

| Figure 13-21 | Auto_C2_ECBC Mode Transfer wieth ADMA                           | 280       |

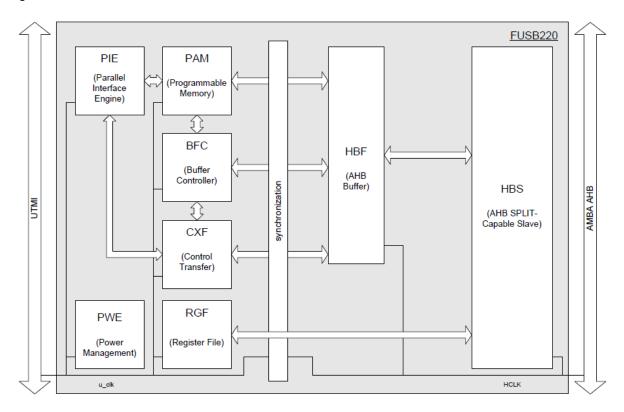

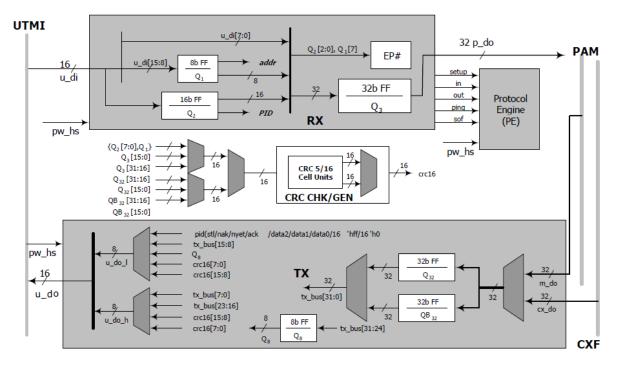

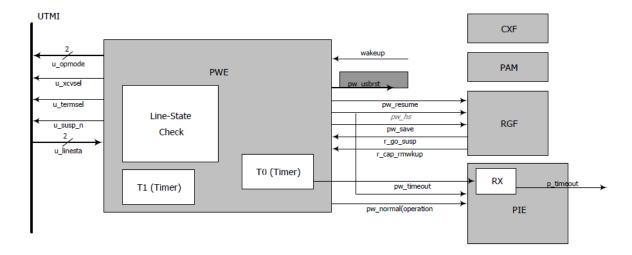

| Figure 14-1  | USB Device Controller                                           | 283       |

| Figure 14-2  | PIE Block Diagram                                               | 284       |

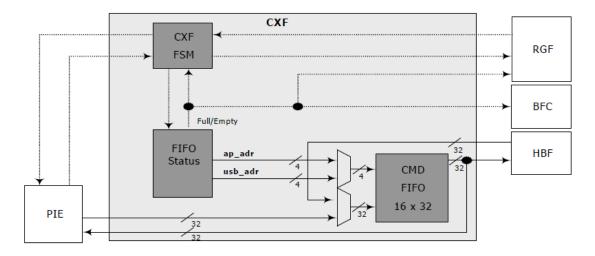

| Figure 14-3  | CXF Block Diagram                                               | 285       |

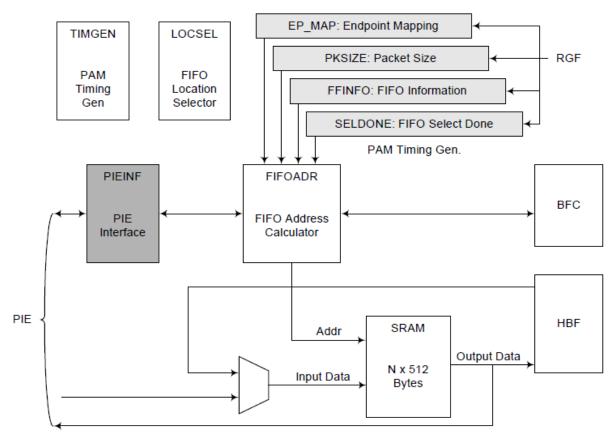

| Figure 14-4  | PAM Block Diagram                                               | 286       |

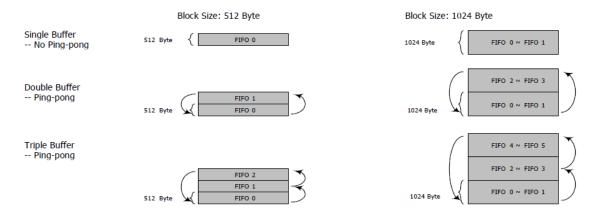

| Figure 14-5  | Ping-Pong FIFO mechanism with different block size and block n  | umber.286 |

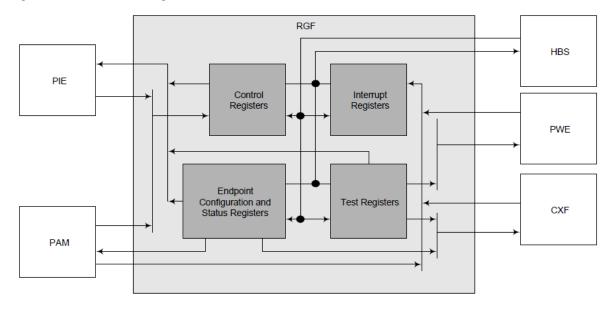

| Figure 14-6  | RGF Block Diagram                                               | 287       |

| Figure 14-7  | PWE Block Diagram                                               | 288       |

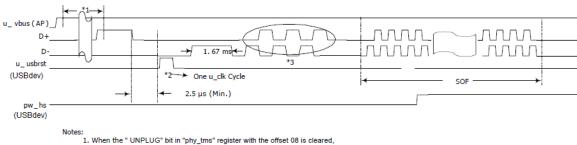

| Figure 14-8  | Timing Diagram of USB Reset and High-speed Detection Handsl     | nake289   |

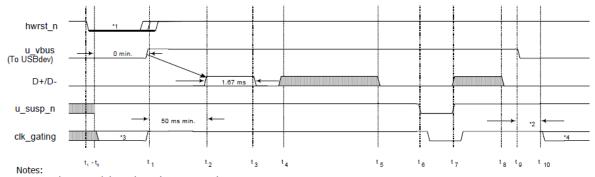

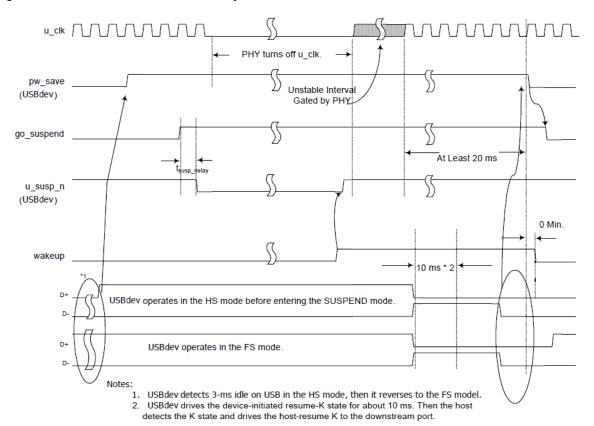

| Figure 14-9  | USB Device Controller Asserts internal u_susp_n to Turn Off the | PLL in    |

|              | PHY                                                             | 290       |

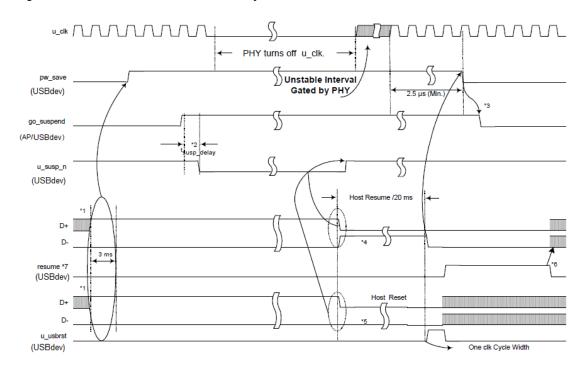

| Figure 14-10 | USB Device Controller Woken by Host Resume/Reset                | 291       |

| Figure 14-11 | USB Device Controller Woken by AP                               | 292       |

| Figure 14-12 | Timing Diagram of t <sub>susp_delay</sub> Programing            |           |

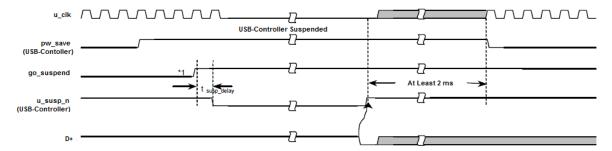

| Figure 16-1  | Block diagram of DMA Controller                                 | 340       |

# **List of Figures**

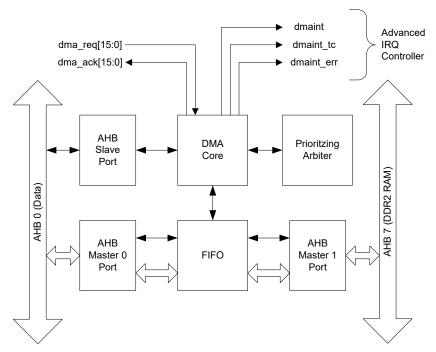

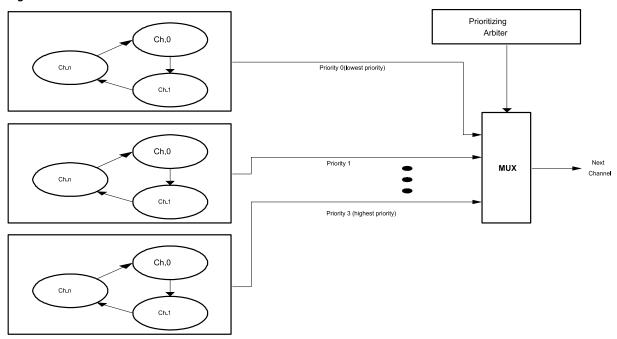

| Figure 16-2  | Arbitration Scheme                                       | 341 |

|--------------|----------------------------------------------------------|-----|

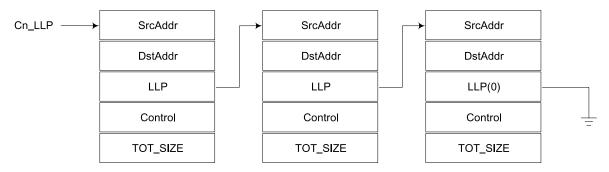

| Figure 16-3  | Linked List Structure of Chain Transfer Operation        | 342 |

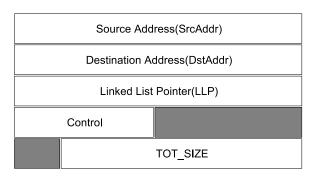

| Figure 16-4  | Linked List Descriptor                                   | 343 |

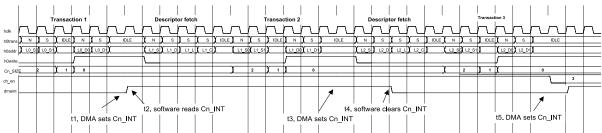

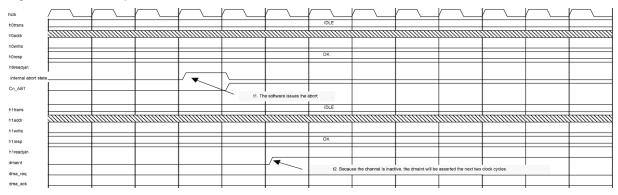

| Figure 16-5  | Interrupt Conflict during Chain Transfer Operation       | 344 |

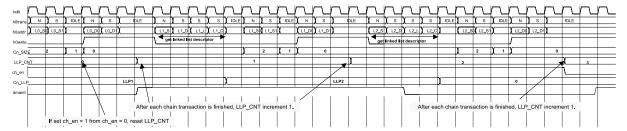

| Figure 16-6  | LLP_CNT Operation                                        | 344 |

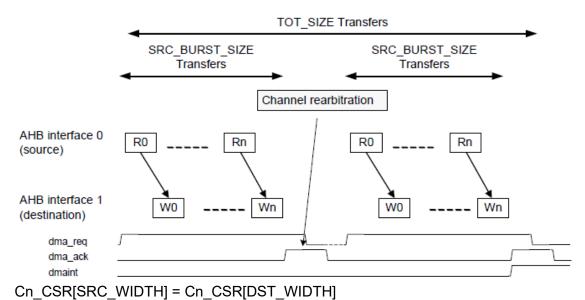

| Figure 16-7  | Example of Hardware Handshake Mode Transfer              | 346 |

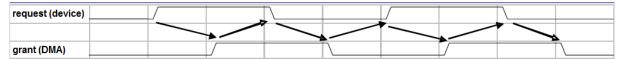

| Figure 16-8  | DMA Hardware Handshake Protocol                          | 346 |

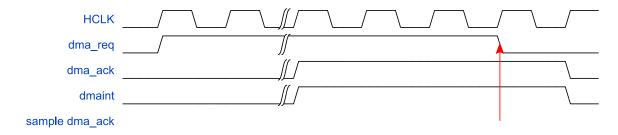

| Figure 16-9  | Error Response of Transfer in Hardware Handshake Mode    | 346 |

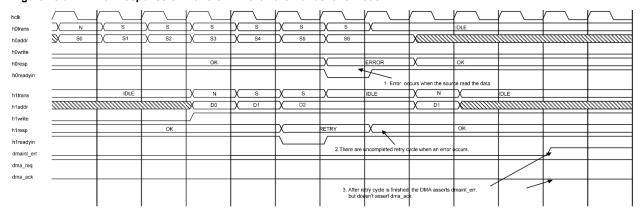

| Figure 16-10 | Abort Operation with Active Channel                      | 347 |

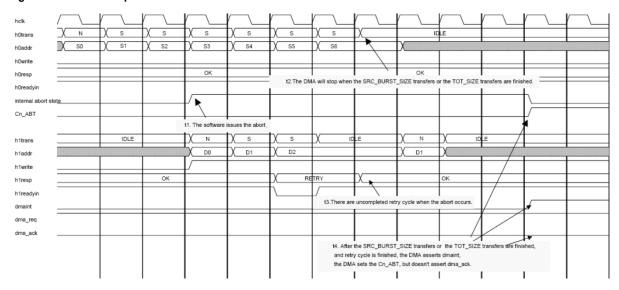

| Figure 16-11 | Abort Operation with Inactive Channel                    | 347 |

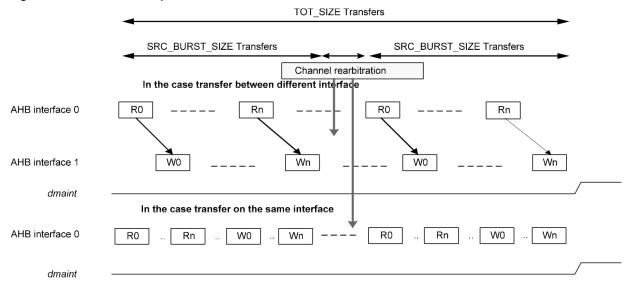

| Figure 16-12 | Transfer Example in DMA Normal Mode                      | 348 |

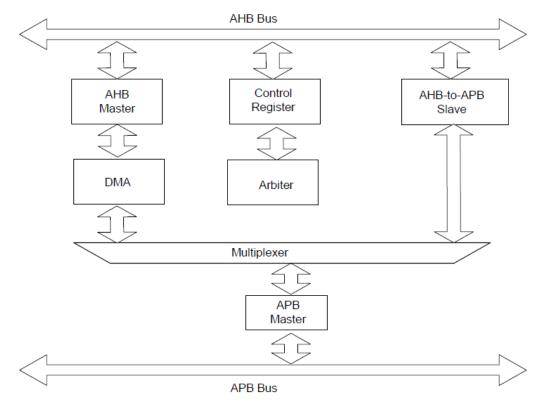

| Figure 17-1  | Functional Block Diagram of APB Bridge                   | 372 |

| Figure 17-2  | Hardware Handshake Protocol                              | 374 |

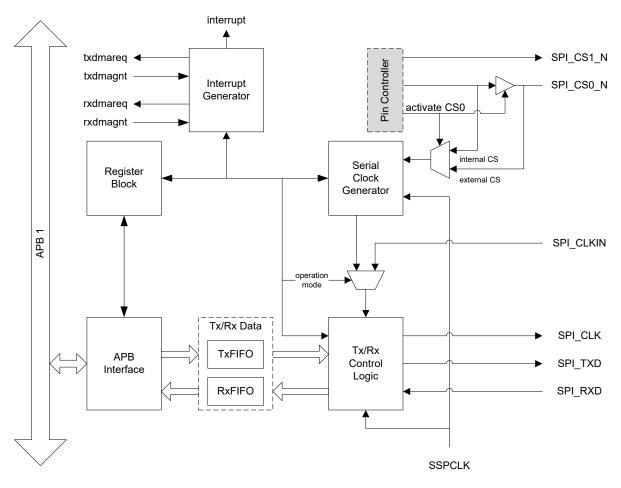

| Figure 18-1  | Block diagram of SPI Controller                          | 382 |

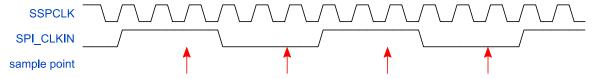

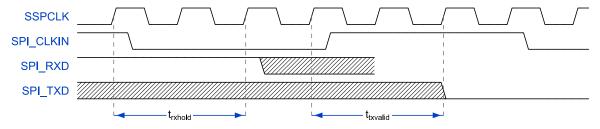

| Figure 18-2  | Relationships among SSPCLK, SPI_CLKIN and Sample Points  | 384 |

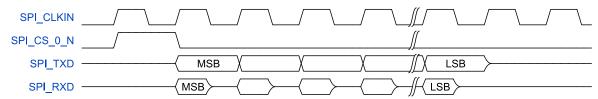

| Figure 18-3  | Single Transfer Using TI SSP Frame Format                | 385 |

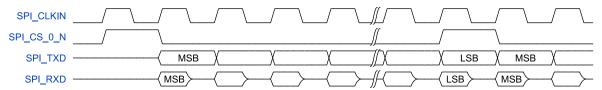

| Figure 18-4  | Continuous Transfer Using TI SSP Frame Format            | 385 |

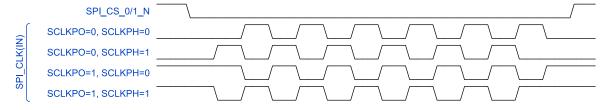

| Figure 18-5  | SPI Frame Format Relation to Different SCLKPH and SCLKPO | 385 |

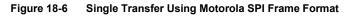

| Figure 18-6  | Single Transfer Using Motorola SPI Frame Format          | 386 |

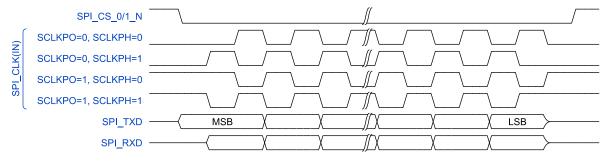

| Figure 18-7  | Continuous Transfer Using Motorola SPI Frame Format      | 386 |

| Figure 18-8  | Setup/Hold Time                                          | 387 |

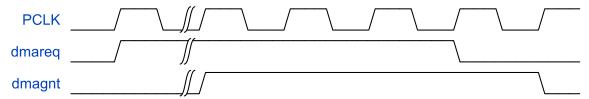

| Figure 18-9  | DMA Interface Timing                                     | 388 |

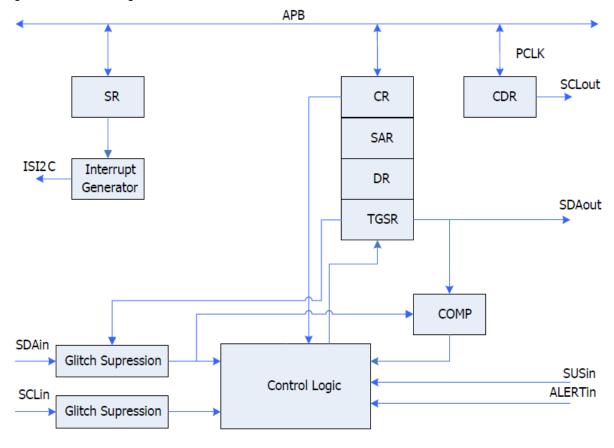

| Figure 20-1  | Block diagram of I <sup>2</sup> C Controller             | 413 |

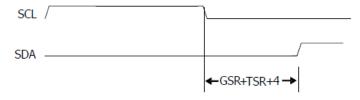

| Figure 20-2  | Relationship among TSR, SCL and SDA                      | 419 |

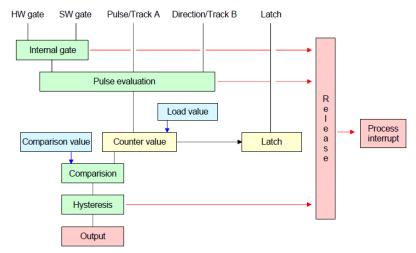

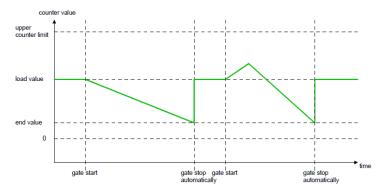

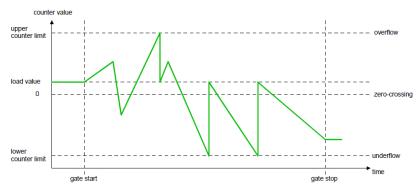

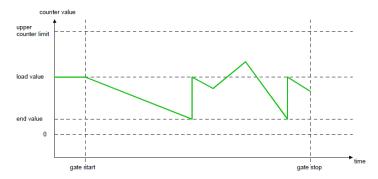

| Figure 23-1  | Counter overview                                         | 459 |

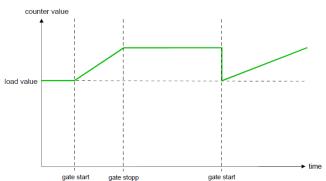

| Figure 23-2  | gate canceled                                            | 460 |

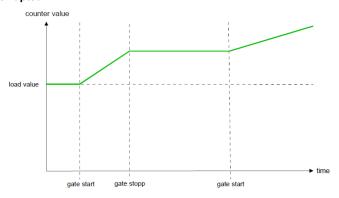

| Figure 23-3  | gate interrupted                                         | 460 |

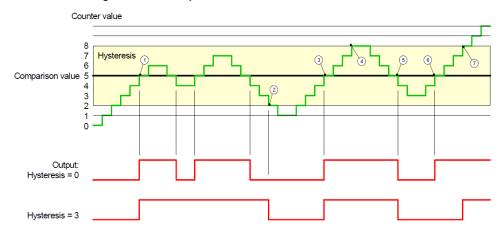

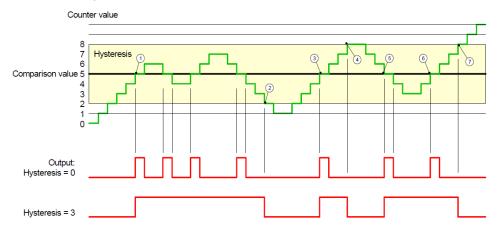

| Figure 23-4  | Counter value greater than compare value                 | 463 |

| Figure 23-5  | Pulse at comparison                                      | 463 |

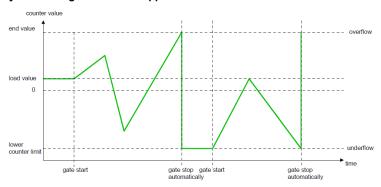

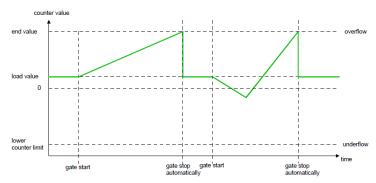

| Figure 23-6  | Count continuously                                       | 464 |

| Figure 23-7  | Single cycle count: gate control stopped                 | 465 |

| Figure 23-8  | Single cycle count: gate control canceled                | 465 |

| Figure 23-9  | Single cycle count: upwards                              | 466 |

| Figure 23-10 | Single cycle count: downwards                            | 466 |

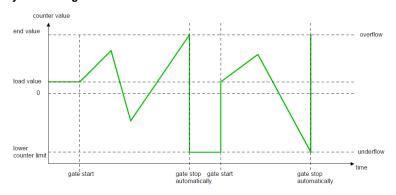

| Figure 23-11 | Periodic count without main direction                    | 467 |

| Figure 23-12 | Periodic count: upwards                                  | 467 |

| Figure 23-13 | Periodic count: downwards                                | 468 |

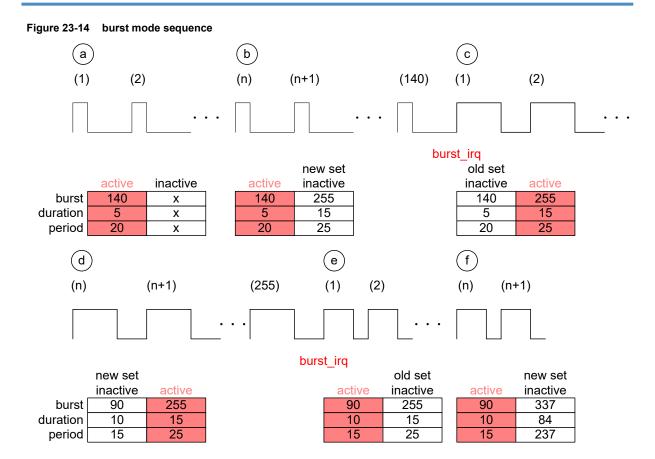

| Figure 23-14 | burst mode sequence                                      | 474 |

# **List of Tables**

| Table 3-1  | AHB/APB Memory Mapping                                       | 30 |

|------------|--------------------------------------------------------------|----|

| Table 4-1  | Pin Controller register mapping                              |    |

| Table 4-2  | Port options                                                 |    |

| Table 6-1  | Summary of Ethernet controller                               | 39 |

| Table 6-2  | Interrupt Status Register                                    |    |

| Table 6-3  | Interrupt Enable Register                                    | 41 |

| Table 6-4  | MAC Most Significant Address Register                        |    |

| Table 6-5  | MAC Least Significant Address Register                       |    |

| Table 6-6  | Multicast Address Hash Table0 Register                       | 42 |

| Table 6-7  | Multicast Address Hash Table1 Register                       | 42 |

| Table 6-8  | Normal Priority Transmit Poll Demand Register                | 42 |

| Table 6-9  | Receive Poll Demand Register                                 | 42 |

| Table 6-10 | Normal Priority Transmit Ring Base Address Register          | 43 |

| Table 6-11 | Receive Ring Base Address Register                           | 43 |

| Table 6-12 | High Priority Transmit Poll Demand Register                  | 43 |

| Table 6-13 | High Priority Transmit Ring Base Address Register            | 43 |

| Table 6-14 | Interrupt Timer Control Register                             | 44 |

| Table 6-15 | Issue a Transmit Interrupt                                   | 45 |

| Table 6-16 | Issue a Receive Interrupt                                    | 46 |

| Table 6-17 | Automatic Polling Timer Control Register                     | 46 |

| Table 6-18 | DMA Burst Length and Arbitration Control Register            | 47 |

| Table 6-19 | DMA/FIFO State Register                                      | 48 |

| Table 6-20 | DMA/FIFO State Register                                      | 49 |

| Table 6-21 | Receive Buffer Size Register                                 | 50 |

| Table 6-22 | Mac Control Register                                         | 51 |

| Table 6-23 | Mac Control Register                                         | 52 |

| Table 6-24 | Test Mode Register                                           | 52 |

| Table 6-25 | PHY Data Register                                            | 53 |

| Table 6-26 | Flow Control Register                                        | 53 |

| Table 6-27 | Back Pressure Register                                       | 54 |

| Table 6-28 | Wake-On-LAN Control Register                                 | 54 |

| Table 6-29 | Wake-On-LAN Status Register                                  | 55 |

| Table 6-30 | Wake-On-LAN Status Register                                  | 55 |

| Table 6-31 | Wake-up Frame Byte Mask 1 <sup>st</sup> Double-word Register | 56 |

| Table 6-32 | Wake-up Frame Byte Mask 2 <sup>nd</sup> Double-word Register | 56 |

| Table 6-33 | Wake-up Frame Byte Mask 3 <sup>rd</sup> Double-word Register | 57 |

| Table 6-34 | Wake-up Frame Byte Mask 4 <sup>th</sup> Double-word Register | 57 |

| Table 6-35 | Normal Priority Transmit Ring Pointer Register               | 58 |

| Table 6-36 | High Priority Transmit Ring Pointer Register                 | 58 |

| Table 6-37 | Receive Ring Pointer Register                                | 58 |

| Table 6-38 | TPKT_CNT Counter Register                                    | 58 |

| Table 6-39 | TXMCOL_CNT and TXSCOL_CNT Counter Register                   |    |

| Table 6-40 | TXECOL_CNT and TXFAIL_CNT Counter Register                   | 59 |

| Table 6-41 | TXLCOL_CNT and TXUNDERRUN_CNT Counter Register      | 59  |

|------------|-----------------------------------------------------|-----|

| Table 6-42 | RPKT_CNT Counter Register                           | 59  |

| Table 6-43 | BROPKT_CNT Counter Register                         | 59  |

| Table 6-44 | MULPKT_CNT Counter Register                         | 60  |

| Table 6-45 | RPF_CNT and AEP_CNT Counter Register                | 60  |

| Table 6-46 | RUNT_CNT Counter Register                           | 60  |

| Table 6-47 | CRCER_CNT and FTL_CNT Counter Register              | 60  |

| Table 6-48 | RCOL_CNT and RLOST_CNT Counter Register             | 61  |

| Table 6-49 | Advance Interrupt Timer Control Register            | 61  |

| Table 6-50 | TXDES0                                              | 65  |

| Table 6-51 | TXDES1                                              | 65  |

| Table 6-52 | TXDES2                                              | 66  |

| Table 6-53 | TXDES3                                              | 66  |

| Table 6-54 | RXDES0                                              | 68  |

| Table 6-55 | RXDES1                                              | 68  |

| Table 6-56 | RXDES2                                              | 69  |

| Table 6-57 | RXDES3                                              | 69  |

| Table 6-58 | Ethernet Address Filtering                          | 70  |

| Table 6-59 | Wake-up Frame Format                                | 72  |

| Table 6-60 | Ethernet Type II                                    | 74  |

| Table 6-61 | IEEE802.3/802.2/SNAP                                | 74  |

| Table 6-62 | PHY Bit Stream Format                               | 78  |

| Table 7-1  | Summary DDR2 Memory Controller Registers            | 86  |

| Table 7-2  | Memory Controller Configuration Register            | 87  |

| Table 7-3  | Memory Controller State Control Register            | 89  |

| Table 7-4  | Mode Register Set Value Register of MR and EMR      | 91  |

| Table 7-5  | Mode Register Set Value Register of EMR 2 and EMR 3 | 91  |

| Table 7-6  | External Rank0/Rank1 Register                       | 91  |

| Table 7-7  | DDR2 Memory Width = 16 bits                         | 92  |

| Table 7-8  | External Rank0/Rank1 Register                       | 92  |

| Table 7-9  | Timing Parameter 1 Register                         | 93  |

| Table 7-10 | Timing Parameter 1 Register                         | 95  |

| Table 7-11 | DDR2 PHY Command and Data Block Control Register    | 96  |

| Table 7-12 | DDR2 PHY Command and Data Block Control Register    | 99  |

| Table 7-13 | COMPBLK Control Register                            | 99  |

| Table 7-14 | COMPBLK Control Register                            | 100 |

| Table 7-15 | Setting for Read/Write Operation                    | 100 |

| Table 7-16 | Channel Arbitration Setup Register                  | 101 |

| Table 7-17 | Channel Arbitration Grant Count RegisterA           | 103 |

| Table 7-18 | Channel Arbitration Grant Count RegisterB           | 103 |

| Table 7-19 | DDR2 PHY Write/Read Data Timing Control Register    |     |

| Table 7-20 | Command Flush Control Register                      | 106 |

| Table 7-21 | Command Flush Status Register                       | 107 |

| Table 7-22 | Command Flush Status Register                       | 107 |

| Table 7-23  | User Defined Register                                  | 108 |

|-------------|--------------------------------------------------------|-----|

| Table 7-24  | DDR2 PHY MISC Control Register1                        | 108 |

| Table 7-25  | Traffic Monitor Clock Cycle Register                   | 108 |

| Table 7-26  | Command Count Register for Channel0                    | 108 |

| Table 7-27  | Command Count Register for Channel1                    | 109 |

| Table 7-28  | Command Count Register for Channel2                    | 109 |

| Table 7-29  | Command Count Register for Channel3                    | 109 |

| Table 7-30  | Command Count Register for Channel4                    | 109 |

| Table 7-31  | Command Count Register for Channel5                    | 109 |

| Table 7-32  | AHB INCR Read Prefetch Length1                         | 110 |

| Table 7-33  | AHB INCR Read Prefetch Length2                         | 111 |

| Table 7-34  | Initialization of Waiting Cycle Count1                 | 111 |

| Table 7-35  | Setting for QoS Command Count                          | 112 |

| Table 7-36  | QoS Control Register                                   | 112 |

| Table 7-37  | QoS Command Count RegisterA                            | 112 |

| Table 7-38  | QoS Command Count RegisterB                            | 113 |

| Table 7-39  | QoS Command Count RegisterC                            | 113 |

| Table 7-40  | QoS Command Count RegisterD                            | 114 |

| Table 7-41  | Channel Arbitration Setup RegisterB                    | 115 |

| Table 7-42  | Channel Arbitration Setup RegisterC                    | 116 |

| Table 7-43  | Channel Arbitration Setup RegisterD                    | 117 |

| Table 7-44  | DDR Phy Read Path DLL Tuning for Falling Edge Register | 117 |

| Table 7-45  | DDR Phy Misc2 Register                                 | 118 |

| Table 7-46  | DDR ELASTIC FIFO Control Register                      | 119 |

| Table 7-47  | CMDADDR Block Clock Tree Control Register              | 119 |

| Table 7-48  | MA Table (AMTSEL=00) in 16-bit DDR2 Mode               | 120 |

| Table 7-49  | MA Table (AMTSEL=01) in 16-bit DDR2 Mode               | 121 |

| Table 8-1   | Bit assignment of the AEI configuration register       | 125 |

| Table 8-2   | Timing values for basic AEI read access                | 126 |

| Table 8-3   | Timing values of AEI read access using AEI_WAIT        | 127 |

| Table 8-4   | Timing values of AEI write access                      | 128 |

| Table 8-5   | Timing values of AEI write access using AEI_WAIT       | 129 |

| Table 8-6   | Calculation of AEI transfer length                     | 130 |

| Table 10-1  | Summary of CAN Registers                               | 133 |

| Table 10-2  | Control Register                                       | 135 |

| Table 10-3  | Status Register                                        | 137 |

| Table 10-4  | Interrupt Register                                     | 138 |

| Table 10-5  | CAN Bit Timing Register                                | 138 |

| Table 10-6  | Standard Bit Timing Parameter                          | 139 |

| Table 10-7  | Global Mask Register                                   | 139 |

| Table 10-8  | Message Object (overview)                              | 140 |

| Table 10-9  | Arbitration Register                                   | 141 |

| Table 10-10 | Message Control Register                               | 142 |

| Table 10-11 | Message Configuration Register                         | 143 |

| Table 10-12 | Media ID Mask Register                                     | 143 |

|-------------|------------------------------------------------------------|-----|

| Table 10-13 | Media Arbitration Register                                 | 143 |

| Table 10-14 | Send Interval Time                                         | 144 |

| Table 10-15 | System Clock Value                                         | 144 |

| Table 10-16 | Receive Delay Timer                                        | 144 |

| Table 10-17 | Data Frame initiated by User (Requestor)                   | 146 |

| Table 10-18 | Automatic Data Frame triggered by Remote Frame (Responder) | 146 |

| Table 10-19 | Manual Data Frame triggered by Remote Frame (Responder)    | 147 |

| Table 10-20 | Receive Data Frame (Responder)                             | 150 |

| Table 10-21 | Remote Frame (Requestor)                                   | 150 |

| Table 10-22 | Interrupt handling                                         | 153 |

| Table 10-23 | Clock Synchronization Events and Intervals                 | 155 |

| Table 10-24 | Coding of Time Object Frame                                | 156 |

| Table 10-25 | Handling Sync Producer                                     | 156 |

| Table 10-26 | Handling Sync Consumer                                     | 156 |

| Table 11-1  | Summary of MicroCode                                       | 163 |

| Table 11-2  | OPCODE                                                     | 164 |

| Table 11-3  | Command Register Setting                                   | 169 |

| Table 11-4  | Copy back with cache                                       | 171 |

| Table 11-5  | Subroutine Command Index                                   | 171 |

| Table 11-6  | Basic I                                                    | 172 |

| Table 11-7  | Basic II                                                   | 172 |

| Table 11-8  | Basic III                                                  | 173 |

| Table 11-9  | 2Plane I                                                   | 173 |

| Table 11-10 | 2Plane II                                                  | 174 |

| Table 11-11 | Interleaving                                               | 174 |

| Table 11-12 | Cache                                                      | 175 |

| Table 11-13 | Misc                                                       | 176 |

| Table 11-14 | DDR                                                        | 177 |

| Table 11-15 | Small Page Read                                            | 177 |

| Table 11-16 | Small Page Write                                           | 177 |

| Table 11-17 | Small Page Misc                                            | 178 |

| Table 11-18 | Command Register Setting for Fixed Flow Command 2          | 178 |

| Table 11-19 | Subroutine Command Index                                   | 179 |

| Table 11-20 | Subroutine Command Index                                   | 179 |

| Table 11-21 | Large page I                                               | 180 |

| Table 11-22 | Large page II                                              | 180 |

| Table 11-23 | Large page III                                             | 180 |

| Table 11-24 | Small page I                                               | 181 |

| Table 11-25 | Small page II                                              | 181 |

| Table 11-26 | Small page III                                             | 181 |

| Table 11-27 | Summary of NAND-Controller Registers                       | 182 |

| Table 11-28 | ECC Status Register                                        | 184 |

| Table 11-29 | ECC Control Register (0x0008)                              | 185 |

| Table 11-30 | ECC Threshold Register (0x0010)                     | 185 |

|-------------|-----------------------------------------------------|-----|

| Table 11-31 | ECC Correction Register (0x0018)                    | 185 |

| Table 11-32 | ECC Interrupt Enable Register                       |     |

| Table 11-33 | ECC Interrupt Status Register                       | 186 |

| Table 11-34 | ECC Status Clear Register                           | 186 |

| Table 11-35 | ECC Status of Spare Region Register                 | 187 |

| Table 11-36 | Spare Region ECC Control Register0 (0x0034)         | 187 |

| Table 11-37 | Spare Region ECC Control Register1 (0x003C)         | 187 |

| Table 11-38 | Device Busy/Ready Status Register                   | 188 |

| Table 11-39 | NANDC General Setting Register                      | 188 |

| Table 11-40 | Memory Attribute Setting Register1                  | 189 |

| Table 11-41 | Memory Attribute Setting Register2                  | 190 |

| Table 11-42 | AC Timing Register0 of NANDC                        | 191 |

| Table 11-43 | AC Timing Register1 of NANDC                        | 192 |

| Table 11-44 | AC Timing Register2 of NANDC                        | 193 |

| Table 11-45 | Summary of AC Timing Usage                          | 194 |

| Table 11-46 | NANDC Interrupt Enable Register                     | 194 |

| Table 11-47 | NANDC Interrupt Enable Register                     | 195 |

| Table 11-48 | Current Access Row Address Channel                  | 195 |

| Table 11-49 | Read Status Register                                | 195 |

| Table 11-50 | Address Toggle Bit Location Register                | 196 |

| Table 11-51 | NANDC Software Reset Register                       | 196 |

| Table 11-52 | NANDC Auto-compare Pattern Register                 |     |

| Table 11-53 | Variable Address Register                           | 197 |

| Table 11-54 | Command Queue Status Register                       | 197 |

| Table 11-55 | Command Queue Flush Register                        | 198 |

| Table 11-56 | Address Toggle Bit Location Register                | 198 |

| Table 11-57 | NANDC Software Reset Register                       | 198 |

| Table 11-58 | Command Queue1 Register                             | 199 |

| Table 11-59 | Command Queue2 Register                             | 199 |

| Table 11-60 | Command Queue3 Register                             | 199 |

| Table 11-61 | Command Queue4 Register                             | 200 |

| Table 11-62 | BMC Region Status Register                          | 201 |

| Table 11-63 | Region User Mode Pointer Adjustment Register        | 202 |

| Table 11-64 | Command Queue1 Register                             | 203 |

| Table 11-65 | Region Software Reset Register                      | 203 |

| Table 11-66 | Force Region Fill Data Register                     | 204 |

| Table 11-67 | Region Remaining Sector Count of Read Data Register | 204 |

| Table 11-68 | AHB Slave Memory Space Range Register               | 204 |

| Table 11-69 | AHB Slave Memory Space Range Register               | 205 |

| Table 11-70 | ECC Correction Capability Register1                 | 205 |

| Table 11-71 | ECC Correction Capability Register2                 | 206 |

| Table 11-72 | ECC Correction Capability Register3                 | 206 |

| Table 11-73 | Programmable OPCODE Register                        | 206 |

| Table 11-74 | Programmable OPCODE Register                               | 206 |

|-------------|------------------------------------------------------------|-----|

| Table 12-1  | Summary of QaudSPI Controller Registers                    | 216 |

| Table 12-2  | Command Queue First Word                                   | 217 |

| Table 12-3  | Command Queue Second Word                                  | 217 |

| Table 12-4  | Command Queue Third Word                                   | 218 |

| Table 12-5  | Command Queue Fourth Word                                  | 218 |

| Table 12-6  | Control Register                                           | 220 |

| Table 12-7  | AC Timing Register                                         | 220 |

| Table 12-8  | Status Register                                            | 220 |

| Table 12-9  | Interrupt Control Register                                 | 221 |

| Table 12-10 | Interrupt Status Register                                  | 221 |

| Table 12-11 | SPI Read Status Register                                   | 222 |

| Table 12-12 | SPI Address Masking Register                               | 222 |

| Table 12-13 | Data Port Register                                         | 222 |

| Table 13-1  | 32-bit Descriptor Table                                    | 227 |

| Table 13-2  | ADMA States                                                | 228 |

| Table 13-3  | Timing Adjustment of SD Interface Output                   | 229 |

| Table 13-4  | C2 Cipher Characteristics                                  | 230 |

| Table 13-5  | SD Card Controller Registers                               | 232 |

| Table 13-6  | SDMA System Address Register                               | 234 |

| Table 13-7  | Block Size Register                                        | 234 |

| Table 13-8  | Block Count Register                                       | 235 |

| Table 13-9  | Argument 1 Register                                        | 235 |

| Table 13-10 | Transfer Mode Register                                     | 236 |

| Table 13-11 | Transfer Command Setting                                   | 236 |

| Table 13-12 | Transfer Mode Register                                     | 237 |

| Table 13-13 | Relationship between Parameter and Names of Response Types | 237 |

| Table 13-14 | Response Register0-3                                       | 238 |

| Table 13-15 | Response Bit Definition of Each Response Type              | 238 |

| Table 13-16 | Response Register0-3                                       | 238 |

| Table 13-17 | Present Status Register                                    | 239 |

| Table 13-18 | Host Control1 Register                                     | 241 |

| Table 13-19 | Power Control Register                                     | 242 |

| Table 13-20 | Block Gap Control Register                                 | 242 |

| Table 13-21 | Clock Control Register                                     | 243 |

| Table 13-22 | Timeout Control Register                                   | 244 |

| Table 13-23 | Software Reset Register                                    | 244 |

| Table 13-24 | Normal Interrupt Status Register                           | 245 |

| Table 13-25 | Error Interrupt Status Register                            | 246 |

| Table 13-26 | Normal Interrupt Status Enable Register                    | 248 |

| Table 13-27 | Error Interrupt Status Enable Register                     | 249 |

| Table 13-28 | Normal Interrupt Signal Enable Register                    | 249 |

| Table 13-29 | Normal Interrupt Signal Enable Register                    | 249 |

| Table 13-30 | Auto CMD12 Error Status Register                           | 250 |

| Table 13-31 | Relationship between CRC Error and Timeout Error for Auto CMD | 251 |

|-------------|---------------------------------------------------------------|-----|

| Table 13-32 | Normal Interrupt Signal Enable Register                       | 251 |

| Table 13-33 | Capabilities 0/1 Register                                     | 251 |

| Table 13-34 | Force Event Register for Auto CMD Error Status                | 253 |

| Table 13-35 | Force Event Register for Error Interrupt Register             | 253 |

| Table 13-36 | ADMA Error Status Register                                    | 254 |

| Table 13-37 | ADMA System Address Register                                  | 254 |

| Table 13-38 | Preset Value Register                                         | 255 |

| Table 13-39 | Speed Mode Selection                                          | 255 |

| Table 13-40 | Preset Value Register Based on Speed Mode                     | 255 |

| Table 13-41 | Host Controller Version Register                              | 255 |

| Table 13-42 | Vendor-defined Register0                                      | 256 |

| Table 13-43 | Vendor-defined Register1                                      | 256 |

| Table 13-44 | Vendor-defined Register2                                      | 257 |

| Table 13-45 | Vendor-defined Register3                                      | 258 |

| Table 13-46 | Vendor-defined Register5                                      | 258 |

| Table 13-47 | Vendor-defined Register6                                      | 258 |

| Table 13-48 | Vendor-defined Register7                                      | 258 |

| Table 13-49 | Vendor-defined Register8                                      | 259 |

| Table 13-50 | Vendor-defined Register9                                      | 259 |

| Table 13-51 | DMA Handshake Enable Register                                 | 259 |

| Table 13-52 | Cipher Mode Control Register                                  | 259 |

| Table 13-53 | Cipher Mode Status Register                                   | 260 |

| Table 13-54 | Cipher Mode Status Register                                   | 261 |

| Table 13-55 | Low Word of Input Data Register                               | 261 |

| Table 13-56 | High Word of Input Data Register                              | 261 |

| Table 13-57 | Low Word of Input Key Register                                | 261 |

| Table 13-58 | High Word of Input Key Register                               | 261 |

| Table 13-59 | Low Word of Output Data Register                              | 262 |

| Table 13-60 | High Word of Output Data Register                             | 262 |

| Table 13-61 | Secret Constant table Data Port                               | 262 |

| Table 14-1  | Summary of USB Controller Registers                           | 293 |

| Table 14-2  | Main Control Register                                         | 296 |

| Table 14-3  | Device Address Register                                       | 297 |

| Table 14-4  | Test Register                                                 | 297 |

| Table 14-5  | SOF Frame Number Register                                     | 298 |

| Table 14-6  | Mask Timer Register                                           | 299 |

| Table 14-7  | Phy Test Mode Selector Register                               | 299 |

| Table 14-8  | Endpoint <i>n</i> Status Registers                            | 300 |

| Table 14-9  | Vendor-specific I/O Status Registers                          | 300 |

| Table 14-10 | CX Configuration and Status Register                          |     |

| Table 14-11 | Sequence for reading a 31-byte packet from CXF FIFO           |     |

| Table 14-12 | Interrupt Group Mask Register                                 |     |

| Table 14-13 | Interrupt Mask Register Byte0                                 |     |

|             | · · · · · · · · · · · · · · · · · · ·                         |     |

| Table 14-14 | Interrupt Mask Register Byte1-4                | 303 |

|-------------|------------------------------------------------|-----|

| Table 14-15 | Interrupt Mask Register Byte5-6                | 304 |

| Table 14-16 | Interrupt Mask Register Byte7                  | 305 |

| Table 14-17 | Receive Zero-length Data Packet Register Byte0 | 306 |

| Table 14-18 | FIFO Empty Byte0                               |     |

| Table 14-19 | Initial Value of Random Pattern                | 307 |

| Table 14-20 | Byte Count of Random Pattern                   | 307 |

| Table 14-21 | Interrupt Group Mask Register                  | 307 |

| Table 14-22 | Interrupt Source Register Byte0                | 308 |

| Table 14-23 | Interrupt Source Register Byte1-4              | 309 |

| Table 14-24 | Interrupt Source Register Byte5-6              | 310 |

| Table 14-25 | Interrupt Source Register Byte7                | 311 |

| Table 14-26 | Isochronous Sequential Error Register Byte0-1  | 313 |

| Table 14-27 | isochronous Sequential Abort Register Byte0-1  | 313 |

| Table 14-28 | Transferred zero-length Register Byte0-1       | 314 |

| Table 14-29 | Idle Counter                                   | 314 |

| Table 14-30 | Endpoint1-8                                    | 315 |

| Table 14-31 | HBF Data Byte Count                            | 315 |

| Table 14-32 | Transferred zero-length Register Byte0-1       | 315 |

| Table 14-33 | Transferred zero-length Register Byte0-1       | 316 |

| Table 14-34 | DMA Mode Enable Register Word                  | 317 |

| Table 14-35 | FIFO0-7 and FIFO14-15 Map Register             | 317 |

| Table 14-36 | FIFO0-15 Configuration Register                | 318 |

| Table 14-37 | DMA Mode Enable Register Word                  | 319 |

| Table 14-38 | DMA Mode Enable Register Word                  | 319 |

| Table 15-1  | Interrupt Sources                              | 323 |

| Table 15-2  | Register Mapping                               | 325 |

| Table 15-3  | Status_LO Register                             | 326 |

| Table 15-4  | Status_HI Register                             | 326 |

| Table 15-5  | EnSet_LO_Pn Register                           | 327 |

| Table 15-6  | EnSet_HI_Pn Register                           | 327 |

| Table 15-7  | EnClear_LO Register                            | 328 |

| Table 15-8  | EnClear_HI Register                            | 328 |

| Table 15-9  | MaskSet_LO Register                            | 329 |

| Table 15-10 | MaskSet_HI Register                            | 329 |

| Table 15-11 | MaskClear_LO Register                          | 330 |

| Table 15-12 | MaskClear_HI Register                          | 330 |

| Table 15-13 | Ack_LO Register                                | 331 |

| Table 15-14 | Ack_HI Register                                | 331 |

| Table 15-15 | IRQIsrVec Register                             | 332 |

| Table 15-16 | IRQInfo Register                               | 332 |

| Table 15-17 | FIQIsrVec Register                             |     |

| Table 15-18 | FIQInfo Register                               |     |

| Table 15-19 | IntIsFIQ_LO Register                           | 334 |

| Table 15-20 | IntlsFIQ_HI Register                                                 | .334 |

|-------------|----------------------------------------------------------------------|------|

| Table 15-21 | IsrVec0 Register                                                     | .335 |

| Table 15-22 | REQ_Status_LO Register                                               | .335 |

| Table 15-23 | REQ_Status_HI Register                                               | .335 |

| Table 15-24 | EXT_INT Configuration Register                                       | .336 |

| Table 15-25 | EXT_INTx_conf                                                        | .336 |

| Table 15-26 | EXT_INT_Status Register                                              | .337 |

| Table 15-27 | μs_Prescaler Register                                                | .337 |

| Table 15-28 | ThrottleMask_LO Register                                             | .338 |

| Table 15-29 | ThrottleMask_HI Register                                             | .338 |

| Table 15-30 | ThrottleTimeInt0 Register                                            | .339 |

| Table 16-1  | DMA Hardware Handshake Requests                                      | .341 |

| Table 16-2  | Address Map for Linked List Descriptor (Base Address: Cn_LPP[31:2]). | .343 |

| Table 16-3  | Control Field Definition in Linked List Descriptor                   | .343 |

| Table 16-4  | Total Transfer Size Definition in Linked List Descriptor             | .343 |

| Table 16-5  | DMA Controller Registers                                             | .349 |

| Table 16-6  | INT Register                                                         | .351 |

| Table 16-7  | INT_TC Register                                                      | .352 |

| Table 16-8  | INT_TC_CLR Register                                                  | .353 |

| Table 16-9  | INT_ERR/ABT Register                                                 | .354 |

| Table 16-10 | INT_ERR/ABT_CLR Register                                             | .355 |

| Table 16-11 | Storage in FIFO                                                      | .368 |

| Table 16-12 | Source Transfers (Source Address Control = increment)                | .368 |

| Table 16-13 | Destination Transfers                                                | .368 |

| Table 17-1  | Source and destination of requests – APB_Bridge1                     | .374 |

| Table 17-2  | Source and destination of requests – APB_Bridge2                     | .374 |

| Table 17-3  | Summary of APB Bridge Registers                                      | .374 |

| Table 17-4  | Base/Size Register of APB Slave07                                    | .375 |

| Table 17-5  | Source Address of DMA Channel Register                               | .376 |

| Table 17-6  | Destination Address of DMA Channel Register                          | .376 |

| Table 17-7  | Cycles of DMA Channel Register                                       | .376 |

| Table 17-8  | Commands of DMA Channels Register                                    | .377 |

| Table 17-9  | APB Control Register                                                 | .378 |

| Table 17-10 | APB Status Register                                                  | .379 |

| Table 18-1  | Special f <sub>sclk</sub> values                                     | .384 |

| Table 18-2  | SCLKDIV Settings and maximum values for SCLK                         | .384 |

| Table 18-3  | SPI Controller Registers                                             | .388 |

| Table 18-4  | SPICR0 Register                                                      | .389 |

| Table 18-5  | settings for chip select polarity in SPI mode                        | .390 |

| Table 18-6  | SPICR1 Register                                                      | .390 |

| Table 18-7  | SPICR2 Register                                                      | .391 |

| Table 18-8  | SPISTATUS Register                                                   | .392 |

| Table 18-9  | INTR_CR Register                                                     | .393 |

| Table 18-10 | INTR_STATUS Register                                                 | .394 |

| Table 19-1  | Summary of UART Registers                                              | 400 |

|-------------|------------------------------------------------------------------------|-----|

| Table 19-2  | UART Quick Overview                                                    | 401 |

| Table 19-3  | Priority of interrupt levels                                           | 402 |

| Table 19-4  | Source of Interrupts                                                   | 402 |

| Table 19-5  | FIFO Control Register                                                  | 403 |

| Table 19-6  | Line Control Register                                                  | 404 |

| Table 19-7  | Line Status Register                                                   | 405 |

| Table 19-8  | eXtended Feature Register                                              | 406 |

| Table 19-9  | Modem Control Register                                                 | 406 |

| Table 19-10 | Modem Status Register                                                  | 407 |

| Table 19-11 | Baud Rate Configuration (Standard Baud Rates)                          | 408 |

| Table 19-12 | Baud Rate Configuration (PROFIBUS Baud Rates)                          | 409 |

| Table 19-13 | Enhanced Feature Register                                              | 410 |

| Table 19-14 | Timeout Timer Configuration Register                                   | 411 |

| Table 20-1  | I <sup>2</sup> C Controller Registers                                  | 414 |

| Table 20-2  | I <sup>2</sup> C Control Register                                      | 415 |

| Table 20-3  | I <sup>2</sup> C Status Register                                       | 416 |

| Table 20-4  | I <sup>2</sup> C Clock Division Register                               | 417 |

| Table 20-5  | I <sup>2</sup> C Data Register                                         | 418 |

| Table 20-6  | I <sup>2</sup> C Slave Address Register                                | 418 |

| Table 20-7  | I <sup>2</sup> C Set/Hold Time and Glitch Suppression Setting Register | 419 |

| Table 20-8  | I <sup>2</sup> C Bus Monitor Register                                  | 419 |

| Table 21-1  | Timer Register Summary                                                 | 422 |

| Table 21-2  | Timern Control Register Bit Description                                | 424 |

| Table 21-3  | Interrupt Status register                                              | 425 |

| Table 21-4  | Interrupt Mask register                                                | 427 |

| Table 21-5  | Interrupt Enable register                                              | 429 |

| Table 21-6  | Interrupt Acknowledge                                                  | 431 |

| Table 21-7  | Tm_Dis_En Register                                                     | 432 |

| Table 21-8  | Watchdog Register Summary                                              | 434 |

| Table 21-9  | Watchdog Control register                                              | 436 |

| Table 21-10 | Watchdog modes                                                         | 436 |

| Table 21-11 | Watchdog reset status                                                  | 437 |

| Table 22-1  | General Purpose I/O Registers                                          | 438 |

| Table 23-1  | Input Mapping                                                          | 442 |

| Table 23-2  | Output Mapping                                                         | 442 |

| Table 23-3  | digital input/output data                                              | 443 |

| Table 23-4  | digital input/output bits                                              | 443 |

| Table 23-5  | Parameter Mapping                                                      | 444 |

| Table 23-6  | Parameter Mapping                                                      | 444 |

| Table 23-7  | alarm_rising_edge                                                      | 445 |

| Table 23-8  | alarm_falling_edge                                                     | 445 |

| Table 23-9  | diag_en_dio                                                            | 446 |

| Table 23-10 | alarm typ tech                                                         | 446 |

| Table 23-11 | alarm_typ_dio                         | 447 |

|-------------|---------------------------------------|-----|

| Table 23-12 | notify_tech                           | 447 |

| Table 23-13 | notify_dio                            | 447 |

| Table 23-14 | ack_tech                              | 448 |

| Table 23-15 | ack_dio                               | 448 |

| Table 23-16 | Palarm_dio0                           | 448 |

| Table 23-17 | Palarm_dio1                           | 448 |

| Table 23-18 | Dalarm_dio0                           | 449 |

| Table 23-19 | Dalarm_dio1                           | 449 |

| Table 23-20 | Dalarm_dio2                           | 450 |

| Table 23-21 | Dalarm_dio2                           | 450 |

| Table 23-22 | Status and configuration Mapping      | 451 |

| Table 23-23 | Parameter Mapping                     | 452 |

| Table 23-24 | count/latch value                     | 452 |

| Table 23-25 | Status register                       | 453 |

| Table 23-26 | control register                      | 454 |

| Table 23-27 | Configuration register                | 455 |

| Table 23-28 | compare value                         | 457 |

| Table 23-29 | load value                            | 457 |

| Table 23-30 | compare value                         | 457 |

| Table 23-31 | count value                           | 458 |

| Table 23-32 | hysteresis value                      | 458 |

| Table 23-33 | main counting direction limits        | 459 |

| Table 23-34 | gate function                         | 460 |

| Table 23-35 | software gate cancel                  | 461 |

| Table 23-36 | software gate interrupt               | 461 |

| Table 23-37 | software/hardware gate cancel         | 461 |

| Table 23-38 | software/hardware gate interrupt      | 461 |

| Table 23-39 | gate control "single count"           | 461 |

| Table 23-40 | count continuously                    | 464 |

| Table 23-41 | count once without main direction     | 465 |

| Table 23-42 | Single cycle count upwards            | 465 |

| Table 23-43 | Single cycle count downwards          | 466 |

| Table 23-44 | Periodic count without main direction | 466 |

| Table 23-45 | Periodic count upwards                | 467 |

| Table 23-46 | Periodic count downwards              | 467 |

| Table 23-47 | Status and configuration Mapping      | 469 |

| Table 23-48 | Parameter Mapping                     | 469 |

| Table 23-49 | Status register                       | 470 |

| Table 23-50 | mode register                         |     |

| Table 23-51 | Period register                       | 471 |

| Table 23-52 | Burst register                        | 472 |

| Table 23-53 | Duration register                     | 472 |

| Table 23-54 | Configuration register                | 472 |

| Table 23-55 | Status and configuration Mapping | 474 |

|-------------|----------------------------------|-----|

| Table 23-56 | Parameter Mapping                | 475 |

| Table 23-57 | SSI_value                        | 475 |

| Table 23-58 | Status register                  | 475 |

| Table 23-59 | delay time register              | 476 |

| Table 23-60 | send clock register              | 476 |

| Table 23-61 | SSI configuration register       | 477 |

| Table 23-62 | irq+/- register                  | 477 |

| Table 23-63 | irq enable register              | 478 |

| Table 23-64 | Status register                  | 479 |

| Table 23-65 | sls compare value                | 479 |

| Table 23-66 | sle compare value                | 479 |

| Table 23-67 | c0 compare value                 | 479 |

| Table 23-68 | c1 compare value                 | 480 |

| Table 23-69 | c2 compare value                 | 480 |

| Table 23-70 | Parameter mapping                | 480 |

| Table 23-71 | diag_en_tech                     | 481 |

| Table 23-72 | alarm_typ_tech                   | 481 |

| Table 23-73 | notify_tech                      | 481 |

| Table 23-74 | ack_tech                         | 482 |

| Table 23-75 | Palarm_tech0                     | 482 |

| Table 23-76 | Palarm_tech1                     | 484 |

| Table 23-77 | Dalarm_tech0                     | 484 |

| Table 23-78 | Dalarm_tech1                     | 485 |

| Table 23-79 | Dalarm_tech2                     | 485 |

| Table 23-80 | Dalarm_tech3                     | 487 |

| Table 23-81 | invert digital input register    | 488 |

| Table 23-82 | delay output byte2 register      | 488 |

| Table 23-83 | delay output byte1 register      | 489 |

| Table 23-84 | delay output byte0 register      | 489 |

| Table 23-85 | basp register                    | 489 |

| Table 23-86 | PWM base time register           | 490 |

| Table 23-87 | Entire techIO mapping            |     |

| Table 24-1  | Revision history                 | 494 |

# 1 Introduction

# 1.1 ARM Cortex-A5 CPU Core

- 288 MHz core speed

- 64 bit AXI

- 32 kByte instruction cache

- 32 kByte data cache

- JTAG debug interface

- ETM, Embedded Trace Macro Cell for real time tracing

- ITM Instrumentation Trace Macrocell

- ETB Embedded Trace Buffer

- AHB DAP (Access internal memory when ARM is running)

- Little endian byte ordering

- 64 bit Floating Point Unit (No NEON)

# 1.2 Advanced Real-Time Ethernet Switch

- 3 port switch system to connect two external Ethernet ports with one internal port

- Flexible architecture based on a micro-coded 5-core Protocol Processor Unit (PPU) cluster

- Primary focus on dedicated support of Profinet IRT IO, EtherCAT and Mechatrolink-III

- Secondary focus on providing a fast and flexible hardware platform for later (microcode and software stack based) implementation of other Ethernet based protocols

#### • Profinet IO IRT Device (software in development)

Profinet IO IRT specification v2.3 Conformance Class C; Real Time Class 3 Cycle times down to 31,25µs Stack partner: Molex

#### • Mechatrolink-III (software in development)

Mechatrolink-III Master implementation Mechatrolink-III Slave implementation

#### • EtherCAT Slave (software in development)

EtherCAT Slave Stack by ETG/Beckhoff

## • other Ethernet protocols with special HW requirements

General IEEE1588V2 support for EtherNet/IP CIP Sync Ethernet Powerlink Sercos III

#### • other Ethernet protocols without special requirements

Modbus TCP EtherNet/IP

# 1.3 Integrated 100BaseTX Ethernet PHYs (2x)

- 2 integrated 100BaseTX Ethernet PHYs

- 100BaseFX support

- Special adaptions made to address profichip's real-time requirements

# 1.4 SNAP+ (SliceBus) Master

(To be used in combination with SNAP+ ASIC)

#### **Basic SliceBus information:**

- Single master system

- Up to 64 slaves (SNAP+ modules)

- Asynchronous, serial data transmission with 48 MBit/s via point-to-point LVDS physics

#### Error detection mechanism:

- CRC code with Hamming distance 4 for every telegram (all 3 bit errors will be detected)

- Watchdog function inside every SNAP+ module for SNAP+ Master observation

- "Auto shut down" in case of SNAP+ Master malfunction

- Retry statistic for early detection of possible transmission issues

#### **Time-Synchronisation:**

- Every SNAP+ module has its own clock with 1µs resolution

- All SNAP+ module clocks are synchronized with the SNAP+ Master (accuracy <100ns)</li>

- Option for clock synchronization from SNAP+ Master to Fieldbus

#### **SNAP+ Features (SliceBus Slave ASIC):**

#### **Technological functions in SNAP+ ASIC:**

- Standard I/O function: 8 DI/DO or 16DI or 16DO with shift register

- Integrated digital input filter function

- Asynchronous event signaling with μs time stamping for advanced SNAP+ modules

- Two advanced counters with AB oversampling, latch, reset, output, hysteresis, compare value, repetitive/endless counting and additional time stamp information

- SSI function with time stamp information (speed calculations: counter difference/time)

- Pulse Width Modulation with 20ns resolution

- Frequency measurement mode

- Special digital I/O time stamp modules (ETS: Edge Time Stamp System) for input edge and output control with 1µs resolution (independent from fieldbus cycle!)

SPI interface in SNAP+ for analog I/O, Safety I/O or serial CP with external MCU:

2.6 MBit/s SPI interface for external microcontroller

- o up to 16 bytes IN / 16 bytes OUT data for external microcontroller

- o up to 192 bytes of parameter data for external microcontroller

- o Alarm function and watchdog function

# 1.5 **Gigabit Ethernet MAC**

- Supports 10/100/1000Mbps mode

- GMII interface

- DMA engine for transmitting and receiving packets with scatter gather list

- Supports IP, TCP, and UDP checksum offloads

- IEEE 802.1Q VLAN tag insertion for packet transmission, VLAN tag detection and removal for packet reception

## 1.6 **DDR2 16 bit Controller**

- 800 MByte/s maximum bandwidth

- 200 MHz clock rate (400 MHz data rate)

- 256 MByte maximum addressable<sup>1)</sup>

- 1 chip select

# 1.7 Asynchronous External Interface (AEI)

- Configurable 8 bit/16 bit master and slave interface (FIFO / CI)

- Setup/Hold/Accesstime/Pause time configurable

- 2 chip selects with 2 MB address range each and independent timings

- 1 dedicated external IRQ for ARM

- 1 dedicated external IRQ for SNAP+ Master synchronization

- Optional WAIT signal

- Slave Mode: Access time: 70ns in fastest mode

## 1.8 FIFO Interface

- FIFO Interface connected to Real-Time Ethernet Switch, internal ARM Processor and AEI Slave

- 48kByte total memory, divided into 256 FIFOs

- 255 IRQ Flags

# 1.9 Consistency Interface (CI)

- Direct connection to the Realtime switch and the AEI Slave

- 8 kByte input + 8 kByte output with consistency control

- Byte reorder function

Examples:

Unaligned endianness change with knowledge of data structure Separate PROFINET IOPS/IOCS from I/O Data if required

\_

<sup>1)</sup> For memory configuration see chapter 4.9 in document ANT1000/1001 Data Sheet

Generate Data areas with different application update cycles (e.g. 1ms and 250µs for IO Data of one device)

8 Process image partitions

# 1.10 **PROFIBUS-DP Master (2x)**

- 2 independent PROFIBUS-DP Master Controller

- Compliant with PROFIBUS standard IEC 61158

- Supported protocols: DP-V0, DP-V1, DP-V2 (DxB, IsoM, ClockSync)

- PROFIBUS Master Stack available from Profichip/Candeo

# 1.11 VPC3+ PROFIBUS-DP Slave

- PROFIBUS slave interface with data rates up to 12 Mbit/s

- Compliant with PROFIBUS standard IEC 61158

- 4 kByte communication RAM

- Supported protocols: DP-V0, DP-V1, DP-V2 (DxB, IsoM, ClockSync)

- Hardware-PLL for DP-V2 IsoM

- Hardware synchronization signal to SNAP+ Master

# 1.12 **CAN Interface (2x)**

- FullCAN controller for data rates up to 1 Mbit/s

- Complies with CAN standard ISO 11898

- Up to 15 messages simultaneously (each with maximum data length)

- · Different message buffers can be combined as FIFO

- Listen only mode (monitoring of the CAN-bus, no acknowledge, no error flags)

- support of clock synchronization between ANTAIOS based stations

## 1.13 NAND Flash Controller

- 8-bit NAND Flash Controller

- DMA capable in conjunction with main DMA controller

- ECC: 16 bit correctable for 512 bytes

# 1.14 QuadSPI Interface

- Maximum 96 MHz per 4-line (max. 384 Mbit/s)

- DMA mode

- Programmable serial bit clock polarity, phase, and frequency

- SPI serial mode, dual mode and quad mode

- additional optional 4<sup>th</sup> address byte (extend address space up to 4096 M)

- 2 chip select lines

# 1.15 SD/MMC Card Controller

• Supports the MMC bus protocol, version 4.3

- Compliant with the SD memory card protocol version 3.0

- Write Protect pin

- · Card Detect pin

- integrated DMA controller

- Built-in generation and check for 7-bit and 16-bit CRC data

- 1 kByte FIFO buffer

- 4-bit mode

- Up to 25 MByte data transfer

# 1.16 USB 2.0 Device Controller

- USB 2.0 high speed device controller (480Mbit/s)

- 8 endpoints

- Integrated USB PHY

# 1.17 Advanced IRQ Controller

- 8 priority levels

- Round-Robin option for IRQs with the same priority

- · Throttling option for every IRQ channel

- All IRQs can be masked

- 32-bit ISR vector for each IRQ

- Configurable input filters for external IRQs

- IRQ/FIQ selectable for each IRQ channel

# 1.18 Main DMA Controller

- Scatter/Gather capable with chained transfer (linked list)

- 8 DMA channels

- Configurable arbitration schemes

- Support for fixed source address (read from auto-increment-register) to memory

- Support for reading from 8 bit device and copy to 32 bit device

# 1.19 AHB/APB Bridge (2x)

• 4 DMA channels

# 1.20 **SPI Interface**

- Master Mode with up to 80 Mbit/s

- Slave Mode with up to 24 Mbit/s

- DMA mode in conjunction with APB-Bridge

- Programmable frame/sync. polarity

- Programmable serial bit clock polarity, phase, and frequency

- Programmable serial bit data sequence (MSB or LSB first)

- 2 chip select lines

# 1.21 **UART (2x)**

#### Standard features (compatible to 16C550):

- 5/6/7/8 data bits

- 1/1.5/2 stop bits

- None/odd/even/stick parity

- Register/FIFO mode

- Line break generation & detection

- Programmable baud rate generator

- Fully prioritized interrupt system controls

- Status reporting capabilities

- Modem control functions

- Loopback mode

#### **Enhanced Features:**

- High speed mode for higher baud rates up to 12 Mbit/s

- Module controlled activation/deactivation for RTS

- 32-byte FIFO with 16C650 DMA behavior

- DMA mode in conjunction with APB-Bridge

- Enable/disable receiver

- IRQ generation by extended timeout control/detection

- IRQ generation by two configurable ETX characters

- IRQ generation by receive byte counter

- IRQ generation by transmitter with selectable "THR empty" or "TSR empty"

## 1.22 I<sup>2</sup>C Interface

- Master or slave for the I<sup>2</sup>C bus

- Data is transmitted to and received from the I<sup>2</sup>C bus via a buffered interface

- Supports the standard and fast modes

- Supports the 7-bit, 10-bit, and general-call addressing modes

- Glitch suppression by debounce circuit

- Programmable slave address

- Supports the master-transmit, master-receive, slave-transmit, and slave-receive modes

- Supports the multi-master mode

- General-call address detection in the slave mode

# 1.23 Timer and Watchdog Module

#### Timer

- Six independent 32-bit timer with pre-scaler (10ns 80ns selectable)

- Interrupt can be issued upon overflow and time-up

- Each timer has two compare registers

- Supports increment and decrement modes

- Six interrupt sources, one for each counter/timer

- Supports single-shot and free running mode

Automatically reloaded when reaching zero

#### Watchdog

- 32-bit down counter with pre-scaler

- Access protection

- Mode 1: system reset or IRQ at watchdog event

- Mode 2: watchdog IRQ at first watchdog event, system reset at next watchdog event (can be used for debugging)

- Option to pass information through the system reset: two registers with POWER-ON-RESET only (not affected by watchdog-reset)

# 1.24 Boot Code

- Boot option selectable by GPIOs

- Boot from QuadSPI NOR Flash

- Boot from NAND Flash

- Boot from UART 1

- Boot from parallel NOR Flash

# 1.25 **Technology Function Module (Techlo)**

- Maximum 26 bits input and 20 bits output (shared with other interfaces)

- Configurable digital input low pass filter

- Up to 4 counter channels with quadruple evaluation for incremental encoders

- Up to 4 PWM channels (Pulse Width Modulation)

- Up to 2 SSI encoder interfaces

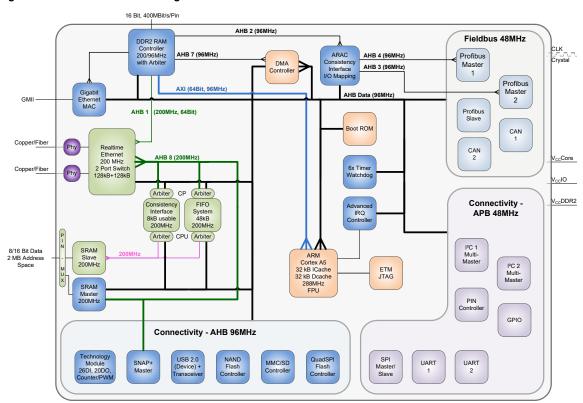

# 2 Block Diagram

Figure 2-1 ANTAIOS Block Diagram

# 3 AHB/APB Memory Mapping

Table 3-1 AHB/APB Memory Mapping

| AHB Slave ID | Component                                 |                                      | Notes                     | Address   |

|--------------|-------------------------------------------|--------------------------------------|---------------------------|-----------|

| 0            | AHB Controller Configuration              |                                      |                           | 0xB800000 |

| 1            | DDR RAM                                   | 16Bit Interface                      |                           | 0x0000000 |

| 5            | Profibus Master 1                         |                                      |                           | 0x4800000 |

| 6            | Profibus Master 2                         |                                      |                           | 0x5000000 |

| 7            | Gigabit MAC                               | 10/100/1000Mbps                      |                           | 0x5800000 |

| 9            | Profibus/CAN                              | VPC3+                                |                           | 0x6800000 |

|              |                                           | CAN 1                                |                           | 0x6A00000 |

|              |                                           | CAN 2                                |                           | 0x6C00000 |

| 10           | AHB to APB Bridge 1                       | UART 2                               | (APB1 ID0)                | 0x7000000 |

|              |                                           | I <sup>2</sup> C 1                   | (APB1 ID2)                | 0x7100000 |